# 17th International Workshop on Worst-Case Execution Time Analysis

WCET 2017, June 27, 2017, Dubrovnik, Croatia

Edited by Jan Reineke

OASIcs - Vol. 57 - WCET 2017

www.dagstuhl.de/oasics

Editor

Jan Reineke Saarland University Saarland Informatics Campus Saarbrücken Germany reineke@cs.uni-saarland.de

ACM Classification 1998 B.8.2 Performance Analysis and Design Aids, C.3 Real-Time and Embedded Systems, D.2.4 Software/ Program Verification, D.4.7 [Organization and Design] Real-Time Systems and Embedded Systems

## ISBN 978-3-95977-057-6

Published online and open access by Schloss Dagstuhl – Leibniz-Zentrum für Informatik GmbH, Dagstuhl Publishing, Saarbrücken/Wadern, Germany. Online available at http://www.dagstuhl.de/dagpub/978-3-95977-057-6.

Publication date June, 2017

Bibliographic information published by the Deutsche Nationalbibliothek The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

#### License

This work is licensed under a Creative Commons Attribution 3.0 Unported license (CC-BY 3.0): http://creativecommons.org/licenses/by/3.0/legalcode.

In brief, this license authorizes each and everybody to share (to copy, distribute and transmit) the work under the following conditions, without impairing or restricting the authors' moral rights: Attribution: The work must be attributed to its authors.

The copyright is retained by the corresponding authors.

Digital Object Identifier: 10.4230/OASIcs.WCET.2017.0

ISBN 978-3-95977-057-6

ISSN 1868-8969

http://www.dagstuhl.de/oasics

## OASIcs - OpenAccess Series in Informatics

OASIcs aims at a suitable publication venue to publish peer-reviewed collections of papers emerging from a scientific event. OASIcs volumes are published according to the principle of Open Access, i.e., they are available online and free of charge.

### Editorial Board

- Daniel Cremers (TU München, Germany)

- Barbara Hammer (Universität Bielefeld, Germany)

- Marc Langheinrich (Università della Svizzera Italiana Lugano, Switzerland)

- Dorothea Wagner (*Editor-in-Chief*, Karlsruher Institut für Technologie, Germany)

### ISSN 2190-6807

## http://www.dagstuhl.de/oasics

## **Contents**

| Preface                                                                                                                                                                                                                                                                                                                                                                                           |                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Jan Reineke                                                                                                                                                                                                                                                                                                                                                                                       | 0:vii               |

| Committee                                                                                                                                                                                                                                                                                                                                                                                         |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                   | 0:ix                |

| Regular Papers                                                                                                                                                                                                                                                                                                                                                                                    |                     |

| STR2RTS: Refactored StreamIT Benchmarks into Statically Analyzable Parallel<br>Benchmarks for WCET Estimation & Real-Time Scheduling<br>Benjamin Rouxel and Isabelle Puaut                                                                                                                                                                                                                        | 1:1-1:12            |

| Best Practice for Caching of Single-Path Code<br>Martin Schoeberl, Bekim Cilku, Daniel Prokesch, and Peter Puschner                                                                                                                                                                                                                                                                               | $2{:}1{-}2{:}12$    |

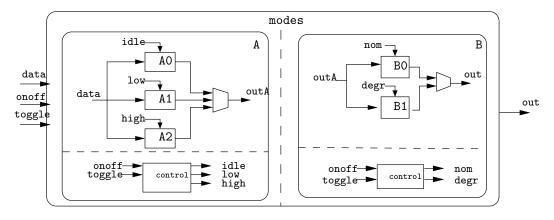

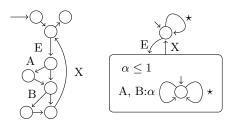

| On the Representativity of Execution Time Measurements: Studying Dependence<br>and Multi-Mode Tasks                                                                                                                                                                                                                                                                                               | 0.1 0.10            |

| Fabrice Guet, Luca Santinelli, and Jerome Morio                                                                                                                                                                                                                                                                                                                                                   | 3:1-3:13            |

| Tightening the Bounds on Cache-Related Preemption Delay in Fixed Preemption         Point Scheduling         Filip Marković, Jan Carlson, and Radu Dobrin                                                                                                                                                                                                                                         | 4:1-4:11            |

| Early WCET Prediction using Machine Learning<br>Armelle Bonenfant, Denis Claraz, Marianne de Michiel, and Pascal Sotin                                                                                                                                                                                                                                                                            | 5:1-5:9             |

| Worst-Case Execution Time Analysis of Predicated Architectures<br>Florian Brandner and Amine Naji                                                                                                                                                                                                                                                                                                 | $6:1-\!\!-\!\!6:13$ |

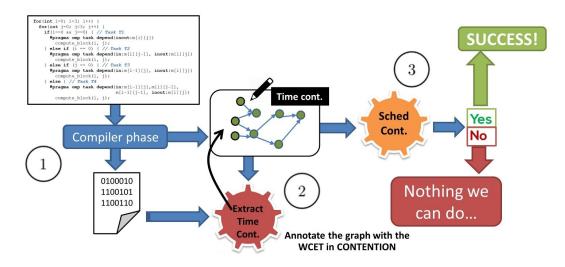

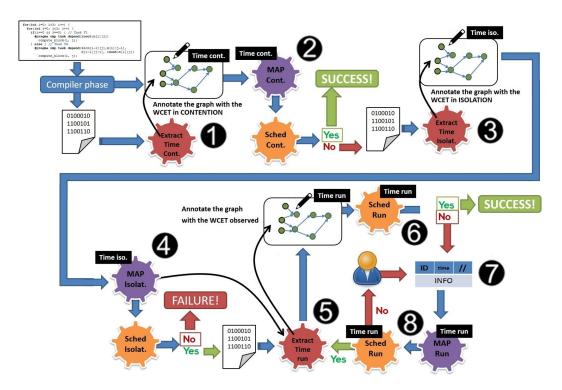

| Towards Multicore WCET Analysis<br>Simon Wegener                                                                                                                                                                                                                                                                                                                                                  | $7{:}1{-}7{:}12$    |

| The Heptane Static Worst-Case Execution Time Estimation Tool<br>Damien Hardy, Benjamin Rouxel, and Isabelle Puaut                                                                                                                                                                                                                                                                                 | 8:1-8:12            |

| The W-SEPT Project: Towards Semantic-Aware WCET Estimation<br>Claire Maiza, Pascal Raymond, Catherine Parent-Vigouroux, Armelle Bonenfant,<br>Fabienne Carrier, Hugues Cassé, Philippe Cuenot, Denis Claraz, Nicolas Halbwachs,<br>Erwan Jahier, Hanbing Li, Marianne De Michiel, Vincent Mussot, Isabelle Puaut,<br>Christine Rochange, Erven Rohou, Jordy Ruiz, Pascal Sotin, and Wei-Tsun Sun. | 9:1-9:13            |

| The P-SOCRATES Timing Analysis Methodology for Parallel Real-Time<br>Applications Deployed on Many-Core Platforms<br>Vincent Nelis, Patrick Meumeu Yomsi, and Luís Miguel Pinho                                                                                                                                                                                                                   | 10:1-10:9           |

| Process 1 cos, 1 where Weather 10 host, and Dato Weyard 1 hill                                                                                                                                                                                                                                                                                                                                    | 10.1 10.3           |

## Preface

It is my pleasure to welcome you to the proceedings of the 17th International Workshop on Worst-Case Execution Time Analysis (WCET 2017). This year the proceedings are published prior to the workshop in order to further stimulate interaction among participants at the event. WCET 2017 is going to take place in Dubrovnik, Croatia as a satellite event of the 29th Euromicro Conference on Real-Time Systems (ECRTS 2017), the premier European venue for research in the broad area of real-time and embedded systems.

The goal of the workshop is to bring together people from academia, tool vendors and users in industry who are interested in all aspects of timing predictability of real-time systems. This is reflected by the makeup of the program committee, as well as the authors of the papers in the proceedings, which consists of academic researchers, tool vendors, and colleagues from industry. This year we received 14 high-quality submissions, out of which the program committee selected 10 for presentation at the workshop and for publication in the proceedings. These papers cover a broad range of timely topics, including, among others, parallel real-time benchmarks, early-stage WCET prediction using machine learning, and approaches to multi-core WCET analysis. I hope that you will find the program interesting and inspiring for your future work!

Putting together this year's workshop program was a team effort. First of all, I would like to thank the authors for their submissions. The program committee and the external reviewers did a great job in evaluating the submissions and in providing constructive feedback to the authors. Thank you for that! I am also grateful to the ECRTS 2017 general chair, Martina Maggio and her team, and the Real-Time Technical Committee Chair of Euromicro, Gerhard Fohler, for their support in organizing the workshop. Thank you also to the team at Schloss Dagstuhl, in particular Marc Herbstritt, for their help in preparing these proceedings.

I am looking forward to welcoming you to WCET 2017 in Dubrovnik! I encourage all participants to embrace the opportunity for discussion and interaction with the authors and other workshop attendees.

Saarbrücken, May 26, 2017 Jan Reineke

## Committee

## **Program Chair**

Jan Reineke – Saarland University, Germany

## **Program Committee**

- Sebastian Altmeyer University of Amsterdam, Netherlands

- Clément Ballabriga Lille 1 University, France

- Florian Brandner Télécom ParisTech, France

- Hugues Cassé IRIT Université de Toulouse, France

- Francisco J. Cazorla Barcelona Supercomputing Center, Spain

- Heiko Falk Hamburg University of Technology, Germany

- Niklas Holsti Tidorum Ltd, Finland

- Claire Maïza Grenoble INP/Verimag, France

- Kartik Nagar Purdue University, United States

- Luis Miguel Pinho CISTER Research Centre/ISEP, Portugal

- Dumitru Potop Butucaru INRIA Rocquencourt, France

- Wolfgang Puffitsch Oticon A/S, Denmark

- Peter Puschner Vienna University of Technology, Austria

- Martin Schoeberl Technical University of Denmark, Denmark

- Benoît Triquet Airbus Group, France

## **External Reviewers**

- Pedro Benedicte Barcelona Supercomputing Center, Spain

- Sebastian Hahn Saarland University, Germany

- Farouk Hebbache CEA LIST, France

- Michael Jacobs Saarland University, Germany

- Suzana Milutinovic Barcelona Supercomputing Center, Spain

- Amine Naji ENSTA ParisTech, France

- Dominic Oehlert Hamburg University of Technology, Germany

## **Steering Committee**

- Guillem Bernat Rapita Systems Ltd., United Kingdom

- Björn Lisper Mälardalen University, Sweden

- Isabelle Puaut University of Rennes I/IRISA, France

- Peter Puschner Vienna University of Technology, Austria

# STR2RTS: Refactored StreamIT Benchmarks into Statically Analyzable Parallel Benchmarks for WCET Estimation & Real-Time Scheduling

Benjamin Rouxel<sup>1</sup> and Isabelle Puaut<sup>2</sup>

- 1 University of Rennes 1, Rennes, France benjamin.rouxel@irisa.fr

- 2 University of Rennes 1, Rennes, France isabelle.puaut@irisa.fr

### - Abstract -

We all had quite a time to find non-proprietary architecture-independent exploitable parallel benchmarks for Worst-Case Execution Time (WCET) estimation and real-time scheduling. However, there is no consensus on a parallel benchmark suite, when compared to the single-core era and the Mälardalen benchmark suite [11]. This document bridges part of this gap, by presenting a collection of benchmarks with the following good properties: (i) easily analyzable by static WCET estimation tools (written in structured C language, in particular neither goto nor dynamic memory allocation, containing flow information such as loop bounds); (ii) independent from any particular run-time system (MPI, OpenMP) or real-time operating system. Each benchmark is composed of the C source code of its tasks, and an XML description describing the structure of the application (tasks and amount of data exchanged between them when applicable). Each benchmark can be integrated in a full end-to-end empirical method validation protocol on multi-core architecture. This proposed collection of benchmarks is derived from the well known StreamIT [21] benchmark suite and will be integrated in the TACleBench suite [10] in a near future. All these benchmarks are available at https://gitlab.inria.fr/brouxel/STR2RTS.

1998 ACM Subject Classification C.3 Real-Time and Embedded Systems

Keywords and phrases Parallel benchmarks, Tasks scheduling, Worst-Case Execution Time estimation

Digital Object Identifier 10.4230/OASIcs.WCET.2017.1

#### 1 Motivations

In the past, the benchmark suite provided by the Mälardalen institute [11] has been widely accepted by the community studying the Worst-Case Execution Time (WCET) of realtime applications on single-core architectures. While multi-cores tend to replace mono-core architectures, no consensus emerged on a parallel benchmark suite when studying the Worst-Case Response Time (WCRT) of a parallel application or its global WCET. The main unsatisfied requirement of such a benchmark suite lies on the identification of parallel tasks to benefit from the multiplicity of available cores.

Current research papers on real-time multi-core mapping and scheduling already face this issue and already use representative application codes for validation. However, it is a common practice to use proprietary applications from the automotive or avionic world [1, 18], unfortunately preventing other researchers to replay tests or to compare results.

Several non proprietary parallel benchmarks already exist for the experimental validation of real time systems. However, they have some limitations. Some consist of periodical

© Benjamin Rouxel and Isabelle Puaut: licensed under Creative Commons License CC-BY

17th International Workshop on Worst-Case Execution Time Analysis (WCET 2017).

Editor: Jan Reineke; Article No. 1; pp. 1:1–1:12

**Open Access Series in Informatics**

Open Access Series in mormans OASICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

independent task sets [4, 6] only, with no synchronization/communication between tasks. Some others lack information to perform WCET estimation or scheduling, e.g.: source code [8, 9, 20], dependency representation [16, 13, 2, 19, 12], or are hardware or run-time system dependent. Other studies prefer task set generators for validation, but cannot be used for a full end-to-end experimental validation as they lack source code.

This document aims at providing a collection of parallel benchmarks for experimental evaluation of real-time systems on multi-/many-core architectures. The targeted audience is the real-time system research community at large, including researchers on WCET estimation and real-time scheduling. This document can be of benefit to experts in multi-core scheduling to experiment their techniques for task mapping and scheduling. It can be of benefit to researchers on worst-case execution time estimation, both on single-core architectures, by analyzing each task of the parallel application, and on multi-core architectures through an analysis of the entire parallel application, including for instance analyses of contentions at the shared resources such as bus, cache, etc.

To ease the creation of a collection of benchmarks with all the required information for WCET estimation and scheduling, we started from the StreamIT benchmark suite [21], which consists of a set of Digital Signal Processing (DSP) applications. Such applications consume incoming data and produce outgoing data at a specific rate, which is representative of many real-time applications.

The provided information for each application is an XML file and a C source file. The XML file describes the structure of the application through a directed acyclic graph (identification of tasks and dependencies between them, volume of data to be transmitted between tasks, WCET of tasks on a particular architecture if the benchmark is to be used for real-time scheduling only). The C code contains the source code of each task. The source code is statically analyzable and self-contained, to allow static WCET estimation techniques on any specific architecture, (but obviously other estimation techniques such as probabilistic or measurement-based are not left aside). In particular, the C code contains pragmas expressing loop bounds in the format used in the TACleBench benchmark suite [10]. We plan to integrate them in the TACleBench benchmark suite as it aims to be the reference benchmark suite for WCET estimation at code level for both single-core and multi-/many-core architecture.

The rest of this document is organized as follows. First, Section 2 compares our work with existing benchmark suites. Section 3 presents background knowledge about the StreamIT benchmark suite, which is used as the basis for STR2RTS. Section 4 provides an overview of the provided material, and finally Section 5 gives some qualitative and quantitative information on the provided benchmarks, before concluding in Section 6.

## 2 Related Work

The usefulness of benchmarks for the validation of systems no longer has to be demonstrated. They have been vastly used in the past to experiment new algorithms, new software, or new pieces of hardware. In computer science, there exists hundreds of different benchmark suites with different purposes and different sizes: SPEC CPU 2006, PolyBench [17], ParMiBench [12], UTDSP [13], Parsec [2], JemBench [19], ParaSuite [16], and many more. However very few of them have been engineered for *multi-core real-time* systems. This kind of systems requires more information in the benchmark suite than just the code, typical input data and a description, which is the general provided material. Indeed, to be largely accepted by the real-time community a benchmark suite must include a source code that is statically analyzable, to allow experiments with both static and non-static WCET estimation methods.

### B. Rouxel and I. Puaut

A non-exhaustive list of the requirements for benchmarks targeting real-time embedded systems would include (i) structured self-contained source code – i.e.: no goto, no dynamic memory allocation, no call to external libraries, (ii) statically computable loop bounds or flow facts for loop bounds, (iii) deadlines and periods of tasks. Adding the multi-core constraints to the system would also add new requirements to the benchmark suite, such as the amount of data exchanged between communicating tasks, and a representation of dependencies between tasks if applicable. The benchmark suite should also remain independent from any specific run-time environment (i.e.: OpenMP, MPI, etc.) to be used as easily as possible.

Starting from the single-core era, the Mälardalen benchmark suite [11] has been accepted by the WCET estimation community. It consists of small pieces of key code representing some well-known code structures found in embedded real-time software. Although representative of embedded software, this benchmark suite contains sequential codes only, and the large majority of provided codes are very small.

A common practice to evaluate scheduling strategies is to use task graph generators. They have the benefit to be architecture independent and generate a vast amount of different topologies. Task Graph For Free (TGFF) [9], Synchronous Dataflow 3 (SDF3) [20] can generate task graphs with dependent tasks in a deterministic way, allowing anybody to replay an experiment as long as the configuration parameters are known. UUniFast [4] is an algorithm generating task sets with uniform distribution in a given space. Task graph generators are very useful when the goal is to empirically validate a method on a large variety of task graph topologies. However we all need *concrete* representative applications with code for further empirical validation which is what we aim at providing here.

Three real parallel applications targeting real-time systems are often used as benchmarks – i.e.: Debie1 [7], Papabench [14] and Rosace [15]. All are control applications respectively for a satellite, a drone and a plane. But three concrete applications are not enough. Our objective with the benchmark suite we provide is to enrich the set of applications that can be used to validate multi-core real-time systems, and enlarge the scope of applications to include signal processing applications with dependencies between tasks.

De Bock *et al.* [6] proposed a benchmark generator targeting multi-core platforms. The generator input is sequential code for each task. All tasks are independent. The benchmark generator output is a task-set fitting some requirements. In comparison, the benchmarks we provide include *dependent* tasks and a representation of these dependencies as well as the amount of data exchanged between dependent tasks.

To the best of our knowledge the benchmark suite closest to this work is the StreamIT benchmark suite [21] that we use as a baseline. In the original version of StreamIT, the authors provide a representation of task's dependencies – a task graph – with communication (exchanged tokens) and source code. However, the provided C source code is only sequential, and the generated code is not WCET-friendly as some benchmarks are impossible to statically analyze, i.e. statically extracting loop bounds might not be possible with available tools. In addition, there is nearly no cache reuse, since tasks performing the same function are systematically duplicated in the generated code. Moreover, dynamic memory allocation is used for allocating messages used for inter-task communication. The C version we provide respects the task graph extracted from the original StreamIT tool, with the benefit of allowing static analyses on each function in isolation.

Finally the new TACleBench suite [10] aims at becoming the *de facto* standard benchmark suite for timing analysis. This work will be integrated in TACleBench in order to strengthen the multi-/many-core dimension of this suite.

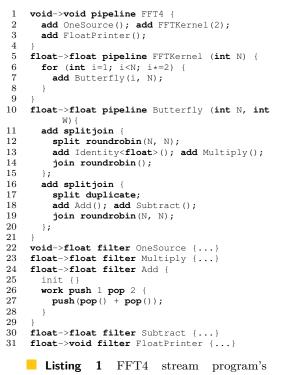

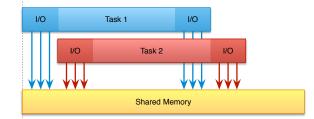

structure.

**Figure 1** FFT4 SDF graph.

## **3** Background on StreamIT

StreamIT [21] is a high-level language for developing *streaming* applications (applications acting on flows of data) modeled as Synchronous Dataflow Graphs (SDF). The StreamIT language has a portable run-time environment and is architecture-independent. The main difference of StreamIT as compared with other streaming languages lies on a required well-defined structure on the streams, that are not an arbitrary network of nodes. One of the major properties of the StreamIT benchmarks lies on the data rate which is imposed to be fixed, thus known at compile time.

All graphs in the StreamIT languages consist of a hierarchical composition of nodes structured in *pipeline*, *split-join* and *feedbackloop* constructs. Streaming applications can then be represented as a Cyclo Static DataFlow graph (CSDF) [3]. They are constructed over the execution of two phases : the *initialization* and the *steady state*, where the latter is considered indefinitely repeating, whereas the former is performed only once and aims at registering the tasks of the steady-state in the StreamIT scheduler.

A streaming application can be seen as a flow of computational units producing and consuming data, the data stream. The basic computational unit of StreamIT applications is the *filter*. Each filter is a task that produces and consumes tokens. Communicating filters are organized in a stream in order to create a *pipeline* (chain) of *filters*. More complex stream structures can be realized with *split-join* and *feedbackloop* constructs. The former splits the data stream in parallel streams before joining them again, whereas the latter re-injects upstream data produced downstream. Conditional control-flow is not allowed at the application level (there is no concept of conditional execution of filters). In contrast, there may be control flow inside filter code. The data stream is propagated through the

### B. Rouxel and I. Puaut

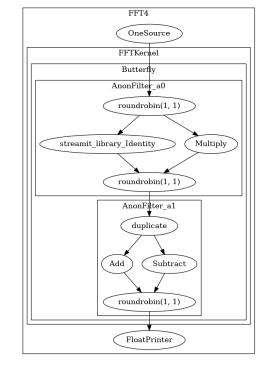

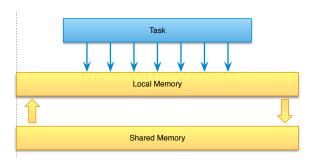

**Figure 2** StreamIT Tool-chain.

filters in the graph at a constant rate known, at compile time. This allows to statically know the amount of data exchanged between filters. Such data are transmitted through dataflow channels implemented as FIFO (First In First Out) queues.

The StreamIT language is illustrated on one of the smallest application from the StreamIT benchmark suite: the radix-2 case of a Fast Fournier Transform (FFT4.str). The application source code in StreamIT language is presented in Listing 1. Lines 1–21 specify the structure of the streaming applications, while lines 22–31 give the source code of the filters (for conciseness only the StreamIT code for filter Add is given).

The first element (line 1: FFT4) is the top-level envelope (equivalent to the main function in C code); it registers three other elements which are added to the global structure (a *pipeline*, i.e. chain of elements for FFT4). Elements are added directly or recursively explored depending of their type. For instance, *OneSource*, line 22 is added directly because it is a simple filter, whereas *Butterfly*, line 10 is explored because it is a composition of elements (here, a pipeline). The code of a very simple filter (*Add*) is given in lines 24–29. It is decomposed into two functions : the *initialization* part (line 25) and the *work* function for the steady-state (lines 26–28). Due to the simplistic nature of this example the initialization part is empty, but one could easily imagine some constant initialization for the steady-state. The *work* function corresponds to the C-like code that will be executed at each iteration of the steady-state. This function calls, at line 27, two functions pop/push to respectively fetch and store data from/to the FIFO channels connected to the previous/next dependent tasks.

The program structure extracted from the StreamIT application from Listing 1 is presented in Figure 1 and it illustrates the steady-state of the application.

The StreamIT benchmark suite comes with an end-to-end compilation tool chain illustrated in Figure 2. It first parses the StreamIT language and generates a Java version of the streaming application. This Java version is then converted to an intermediate representation used by internal tools to analyze the application. Following is a short summary of those tools:

- Partitioning: determining the number of fissions and fusions, used to determine where to insert/remove split-join nodes in the generated code;

- **Mapping:** determining on which core each job implementing a filter will run;

- **Scheduling:** determining in which order jobs will be executed;

- **Code generation:** generating code for the targeted architecture (generally C/C++) through the provision of several back-ends.

The last step generates a code which can be compiled in order to run the application on the targeted architecture (RAW processor, Tilera, RStream and so on). The Java version can

## 1:6 STR2RTS

```

<?xml version="1.0" encoding="UTF-8" ?>

1

2

<appl>

3

tasks

4

<task id="fft4_split2_duplicate" WCET="2286">

<prev id="fft4_join1_round_robin" data-sent="2" data-type="float" />

5

</task>

6

<task id="fft4_join2_weighted_round_robin" WCET="1380">

7

<prev id="fft4_add" data-sent="1"

data-type="float"

8

9

<prev id="fft4_subtract" data-sent="1" data-type="float" />

10

</task>

<task id="fft4_add" WCET="1600">

11

<prev id="fft4_split2_duplicate" data-sent="2" data-type="float" />

12

13

</task>

14

<task id="fft4 subtract" WCET="1600">

<prev id="fft4_split2_duplicate" data-sent="2" data-type="float" />

15

16

</task>

17

<task id="fft4_float_printer" WCET="1614">

<prev id="fft4_join2_weighted_round_robin" data-sent="2" data-type...

18

19

</task>

20

<task id="fft4_one_source" WCET="1198"></task>

21

<task id="fft4_split1_weighted_round_robin" WCET="1380">

22

<prev id="fft4_one_source" data-sent="2" data-type="float" />

23

</task>

24

<task id="fft4_join1_round_robin" WCET="1198">

<prev id="fft4_identity" data-sent="1" data-type="float"

<prev id="fft4_multiply" data-sent="1" data-type="float"</pre>

25

/>

26

27

</task>

28

<task id="fft4_identity" WCET="1054">

29

<prev id="fft4_split1_weighted_round_robin" data-sent="1" data-type...</pre>

30

</task>

<task id="fft4_multiply" WCET="1070">

31

32

<prev id="fft4_split1_weighted_round_robin" data-sent="1" data-type...

</task>

33

34

</tasks>

35

</appl>

```

### **Listing 2** XML representation of the FFT4 application.

also be executed using a simulation library included in the StreamIT project. This simulator runs a sequential version of the streaming application.

Despite the work done on the StreamIT toolchain, none of the provided back-ends generate code ready to be analyzed in the context of real-time systems. The *simpleC* back-end generates only one big main function containing all the code, leading to a sequential version not suitable for multi-core analysis/execution. The *newSimple* back-end generates hard to read and to analyze source code, where it is not possible anymore to identify tasks. The *cluster* back-end generates code that may not be analyzable by loop bound extractors, and includes libraries provided by StreamIT with C++ classes and dynamic memory allocation, thus not suitable for static WCET analysis. In addition, when the same filter is used several times, its code is duplicated, thus degrading the WCET of tasks when considering architectures with caches.

As no back-end fulfills all the requirements implied by real-time systems and corresponding analyses, we modified the StreamIT benchmarks code, as detailed in Section 4.2, to fit the needs of the real-time system community. Among the tools coming with the StreamIT tool chain, we only used the simulation library to ensure that our modifications to the StreamIT codes are functionally equivalent to the original code.

## 4 Benchmarks overview

This section presents an example of the provided information: (i) an XML description, (ii) a C source code ; and how to use it. Then, it presents how this information was extracted from the StreamIT benchmark suite [21].

### B. Rouxel and I. Puaut

### 4.1 **Provided information**

Each benchmark is divided in 4 files, an XML file, a DOT file, a C source file and its corresponding header file. The DOT file is a graphical representation of the tasks and their dependencies using the *graphviz* software<sup>1</sup>, and will not be presented here, as well as the header file. Following is an example of an XML description with its corresponding C source code.

An XML file summarizing all the provided information is presented by Listing 2 and corresponds to our previous example from Figure 1. This file basically describes the structure of the application as a Directed Acyclic Graph (DAG), with tasks as nodes and channels as edges. It can be used by mapping/scheduling tools as input to experimentally evaluate new mapping/scheduling strategies involving either a single application or multiple applications both modeled as DAGs. Another usage, once tasks have been assigned to cores in a multi-core platform, is to use the XML file together with the code of tasks to perform WCET estimation on the application, in particular integrating contentions to access shared resources in the WCET of the application. For each task, the XML file contains the set of predecessors of the task with the amount of data received by each of them, as well as the task WCET. The XML tag *prev* represents task's dependencies as precedences, e.g. line 15 where *Split2DUPLICATE* is a predecessor of *Subtract*. The associated attribute *data-sent* specifies the amount of data needed for one execution of the task, and the attribute *data-type* specified the type of data (e.g. : int, double, float, etc.).

The attribute *WCET* is provided as information for people aiming at performing experiments on mapping/scheduling techniques and do not wishing to perform an initial WCET analysis step. Provided WCETs were estimated by our static WCET analysis tool Heptane [5] for a the MIPS instruction set, for an architecture without caches or pipelines (roughly the provided WCET corresponds to the worst-case number of instructions executed by each task).

Listing 3 introduces the structure of the provided C source code. Each task from the aforementioned graph appears as a C function in the source file. The code of filter/task Add is given as an example in lines 8–14. Depending on the value of  $GLOBAL_N$  (constant evaluated by the C pre-processor), this filter reads two float items from the input channel  $(pop\_float)$ , then sums them before writing the result into the output channel  $(push\_float)$ . The loop is annotated with a pragma specifying the loop bound, according to the TACleBench syntax for flow-facts annotations. The value of  $GLOBAL_N$  has an impact on the number of added tasks (number of added Butterfly from the Listing 1). In the C source code, we fix such parameter in the header file to have the C source code consistent with the XML description. In this example the value of  $GLOBAL_N$  is set to 2.

Lines 22–41 point to the *sequential\_main* function that corresponds to an execution of all tasks on a single-core architecture. Function *sequential\_main* first calls the initialization function of all tasks having a non-empty initialization phase (line 23). This initialization step sets up every C structure, buffers or pre-computed data required by filters for the steady-state run. The *sequential\_main* then calls each filter function in a loop of *MAX\_ITERATION* iterations (lines 28–39) for the steady-state execution. Functions are called in an order that respects dependencies between tasks. This function is provided for users interested in single-core WCET estimation. It was also used to check the correctness of code modifications applied to the StreamIT benchmark, by comparing the results to those produced by the StreamIT Java simulator.

<sup>&</sup>lt;sup>1</sup> http://www.graphviz.org/

```

#include "FFT4.h"

1

2

// GLOBAL_N is defined in the header file and its value is 2

3

4

void fft4_one_source() { ... }

5

void fft4_identity() { ... }

6

void fft4_multiply() { ... }

7

void fft4 add() {

_Pragma ("loopbound min "GLOBAL_N/2" max "GLOBAL_N/2)

9

for(int i=0 ; i < GLOBAL_N/2 ; i++) {</pre>

10

float v1 = pop_float(&AddBuf.buffer_in);

float v2 = pop_float(&AddBuf.buffer_in);

11

push_float(&AddBuf.buffer_out, v1+v2);

12

13

}

14

15

void fft4_subtract() { ... }

16

void fft4_float_printer() { ... }

17

void fft4_init() { ... }

18

void fft4_split1_weighted_round_robin( uint32_t nb ) { ... }

void fft4_join1_round_robin() { ... }

void fft4_split2_duplicate() { ... }

19

20

21

void fft4_join2_weighted_round_robin( uint32_t nb ) { ... }

22

int sequential_main( int argv, char **argc ) {

23

fft4 init();

24

25

for( int i=0 ; i < MAX_ITERATION ; i++ ) {</pre>

26

fft4_OneSource();

_Pragma("loopbound min "(GLOBAL_N/2-1)" max "(GLOBAL_N/2-1))

27

28

for( int j = 1 ; j < GLOBAL_N ; j *= 2 ) {</pre>

29

fft4_split1_weighted_round_robinv(j);

30

fft4_identity();

31

fft4_multiply();

32

fft4_join1_round_robin();

fft4_split2_duplicate();

33

34

fft4 add();

35

fft4_subtract();

36

fft4_join2_weighted_round_robin(j);

37

38

fft4 float printer();

39

40

return EXIT_SUCCESS;

41

```

**Listing 3** C version of the FFT4 stream program.

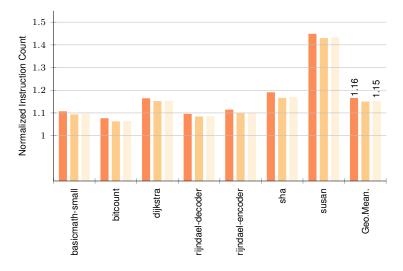

Regarding communications between tasks, a C file implementing the push/pop communication functions has to be provided and linked with the code of each application. Since the implementation of communications is architecture and system dependent, this file has to be provided for every (architecture, system) pair. As a start point we provide a simple implementation of push/pop operations that implement communications through shared memory, using statically allocated FIFO buffers. This simple implementation can be used on single-core architectures and multi-core architectures with shared memory.

## 4.2 Benchmark construction process

In order to extract the above information for each benchmark, we relied on the StreamIT compilation tools as much as possible and we then adapted their output to fit our needs. As presented by the dashed line in Figure 2, we modified the Java pretty-printer to generate a preliminary C version of the streaming application that later needs to be modified manually to match the analysis requirements. When finalizing the C source code through handmade modifications, we stayed independent from any specific run-time library and inter-core communication mechanism. Despite the error proneness of this method, this hand-made step is necessary to guaranty easy read/analyze/understand code with all required annotations. To validate the functional correctness of the final C source version, we performed non-regression tests considering the Java simulator output as the baseline.

#### B. Rouxel and I. Puaut

| Name                      | #tasks    | #split-join | Description                                 |  |

|---------------------------|-----------|-------------|---------------------------------------------|--|

| 802.11a                   | [119;132] | [17;18]     | 802.11a wireless LAN protocol transmitte    |  |

| data rate 6/9/12/18/24/36 |           |             | with different configurations               |  |

| Audiobeam                 | 20        | 1           | Real-time beam-forming                      |  |

|                           |           |             | on a microphone input array                 |  |

| Beamformer                | 56        | 2           | Application to perform beam-forming         |  |

|                           |           |             | on a set of inputs                          |  |

| CFAR                      | 4         | 0           | Constant False Alarm Rate detection         |  |

| Complex-FIR               | 3         | 0           | FIR filter with complex data types          |  |

| DCT2                      | 40        | 2           | Discrete Cosine Transforms                  |  |

|                           |           |             | from Asplos'06 paper super-set              |  |

| DES                       | 423       | 80          | DES encryption algorithm                    |  |

| FFT2                      | 26        | 1           | Fast Fourier Transform, blocked,            |  |

|                           |           |             | coarse-grained version                      |  |

| FFT4                      | 42        | 10          | Fast Fourier Transform, more fine-grained   |  |

| FilterBankNew             | 52        | 1           | Creates a filter bank to perform multi-rate |  |

|                           |           |             | signal processing                           |  |

| FMRadio                   | 43        | 7           | FM radio with multi-band equalizer          |  |

|   | Table 1 | Description | of provided | benchmarks      |

|---|---------|-------------|-------------|-----------------|

| _ | Table 1 | Dependent   | or provided | Southantitating |

To create the XML description, we needed the WCET of each task, the amount of data exchanged between task and the topology of the application's graph. For the first information, we relied on our tool Heptane [5] that gives us the WCET of each task in isolation. The amount of data exchanged and the topology of the graph are extracted manually from files generated by the Java simulator.

## 5 Provided benchmarks

Table 1 summarizes the benchmarks that are ready to use at the time of writing. The first column presents the name of the benchmark (identical to the name in the original StreamIT benchmark suite), followed by the number of tasks, the number of *split-join* nodes and a quick description (also extracted from the original StreamIT benchmark suite). For application 802.11a coming in multiple versions (to be explained later), we provide the minimum and maximum of provided values among all versions.

Table 2 shows the complexity of each benchmark. After the name of the benchmark, the second column shows the width of the graph (the maximum number of tasks at the same topological rank) which gives an idea of the amount of concurrency in the application. Following are information about task's WCET and amount of data exchanged between tasks. Both fields are described with an average and standard deviation.

Table 3 indicates which benchmarks need a *mathematic* library to compile, and use input and/or output file. Nonetheless to ensure self-containment, we provide a dummy implementation (empty shell) for the needed functions.

We found some benchmarks with multiple usages of the same task with different input parameters at different points in the application. We thus generated two versions of each benchmark: one with shared code to allow cache reuse, and another one with duplicated code. The difference between both versions lies on the ability to exploit cache reuse or not, and also accuracy of flow-facts annotations (which are more precise with duplicated code).

### 1:10 STR2RTS

| Name            | Width  | WCET                                   | Data      | #Basic blocks     | #Cond. | #mem.  |

|-----------------|--------|----------------------------------------|-----------|-------------------|--------|--------|

|                 |        | (cycles) (tokens)                      |           | $(avg \ #instr.)$ | br.    | instr. |

|                 |        | <avg, deviation="" standard=""></avg,> |           |                   |        |        |

| 802.11a         | [7;18] | 2.39e5, 6.35e5                         | 596, 2238 | 1584(6)           | 222    | 3519   |

| 6/9/12/18/24/36 |        |                                        |           |                   |        |        |

| Audiobeam       | 15     | 273,1094                               | 3, 5      | 386(7)            | 72     | 893    |

| Beamformer      | 12     | 1.25e4, 9.65e4                         | 4.6, 10   | 459(10)           | 87     | 1188   |

| CFAR            | 1      | 1.58e4, 1.55e4                         | 288, 425  | 375~(6)           | 70     | 821    |

| Complex-FIR     | 1      | 501,655                                | 1.3, 0    | 336~(6)           | 60     | 804    |

| DCT2            | 16     | 1.69e4, 3958                           | 57.6, 91  | 437~(6)           | 86     | 894    |

| DES             | 8      | 2045, 1417                             | 35.7, 29  | 621 (6)           | 111    | 1079   |

| FFT2            | 2      | 2.94e5, 3.03e5                         | 137.8, 49 | 477(6)            | 81     | 1003   |

| FFT4            | 2      | 1337, 450                              | 23.6, 8   | 566~(5)           | 85     | 860    |

| FilterBankNew   | 6      | 6315, 8306                             | 8.9, 11   | 446~(6)           | 84     | 913    |

| FMRadio         | 12     | 1632, 2234                             | 1.6, 1    | 486(6)            | 91     | 1037   |

## **Table 2** Statistics for provided benchmarks.

### **Table 3** Properties of provided benchmarks.

| Name          | Use math library | Use I/O file | Two versions / code reuse |

|---------------|------------------|--------------|---------------------------|

| 802.11a       | yes              | no           | yes                       |

| Audiobeam     | yes              | yes          | no                        |

| Beamformer    | yes              | no           | no                        |

| CFAR          | yes              | no           | no                        |

| Complex-FIR   | no               | yes          | no                        |

| DCT2          | yes              | yes          | no                        |

| DES           | no               | no           | yes                       |

| FFT2          | yes              | no           | no                        |

| FFT4          | no               | no           | no                        |

| FilterBankNew | no               | no           | no                        |

| FMRadio       | yes              | no           | no                        |

The last column of Table 3 indicates whether we created multiple versions of the benchmark with code reuse or not.

Finally, some benchmarks are customizable by modifying the value of some parameters inside the StreamIT source code, e.g. the data rate of the *802.11a* application. As modifying such values has an impact on the application's structure, we generated multiple versions of the same benchmark for the different configurations.

We successfully compiled the list of benchmarks presented in Table 1 for x86\_64 architecture and validated their behavior by comparing their results with the one from the Java simulator provided by StreamIT. All these benchmarks are available at

### https://gitlab.inria.fr/brouxel/STR2RTS.

### 6 Conclusion

This document has presented a collection of benchmarks written in analyzable C language and based on the StreamIT benchmarks suite [21]. The purpose of the refactoring of StreamIT

### B. Rouxel and I. Puaut

applications we have performed is to create self-contained analyzable architecture-independent parallel C applications to allow any kind of experiments on WCET analysis and real-time scheduling on multi-core architectures. To largely spread our work, we will integrate this collection of benchmarks into the TACLeBench project.

Due to the required handmade refactoring, we will be continuously adding new test cases over time while there are still some StreamIT applications to refactor. We foresee the end of refactoring in a couple of year for the 60% remaining benchmarks.

#### — References

- Matthias Becker, Dakshina Dasari, Borislav Nikolic, Benny Akesson, Vincent Nélis, and Thomas Nolte. Contention-free execution of automotive applications on a clustered manycore platform. In *ECRTS*, 2016.

- 2 Christian Bienia. Benchmarking Modern Multiprocessors. PhD thesis, Princeton University, January 2011.

- 3 Greet Bilsen, Marc Engels, Rudy Lauwereins, and Jean A. Peperstraete. Cyclo-static data flow. In Acoustics, Speech, and Signal Processing, 1995. ICASSP-95., 1995 International Conference on, volume 5, pages 3255–3258. IEEE, 1995.

- 4 Enrico Bini and Giorgio C. Buttazzo. Measuring the performance of schedulability tests. *Real-Time Systems*, 30(1-2):129–154, 2005.

- 5 Hardy Damien, Rouxel Benjamin, and Isabelle Puaut. The heptane static worst-case execution time estimation tool. In 17th International Workshop on Worst-Case Execution Time Analysis (WCET 2017), volume 47 of OpenAccess Series in Informatics (OASIcs), 2017. doi:10.4230/OASIcs.WCET.2017.8.

- **6** Yorick De Bock, Sebastian Altmeyer, Jan Broeckhove, and Peter Hellinckx. Task-set generator for schedulability analysis using the taclebench benchmark suite. In *Proceedings of the Embedded Operating Systems Workshop : EWiLi 2016*, pages 1–6. CEUR Workshop proceedings, October 2016.

- 7 Debie1. URL: https://www.irit.fr/wiki/doku.php?id=wtc:benchmarks:debie1.

- 8 Robert Dick. Embedded system synthesis benchmarks suite (E3S), 2010. URL: http: //ziyang.eecs.umich.edu/~dickrp/e3s/.

- 9 Robert P. Dick, David L. Rhodes, and Wayne Wolf. Tgff: task graphs for free. In Proceedings of the 6th international workshop on Hardware/software codesign, pages 97–101. IEEE Computer Society, 1998.

- 10 H. Falk, S. Altmeyer, P. Hellinckx, B. Lisper, W. Puffitsch, C. Rochange, M. Schoeberl, R. Sørensen, P. Wägemann, and S. Wegener. TACLeBench: A benchmark collection to support worst-case execution time research. In *Proceedings of the 16th International Workshop on Worst-Case Execution Time Analysis (WCET'16)*, volume 55 of *OpenAccess Series in Informatics (OASIcs)*, pages 1–10. Schloss Dagstuhl – Leibniz-Zentrum fuer Informatik, 2016. doi:10.4230/0ASIcs.WCET.2016.2.

- 11 Jan Gustafsson, Adam Betts, Andreas Ermedahl, and Björn Lisper. The Mälardalen WCET benchmarks – past, present and future. In Bj"orn Lisper, editor, 10th International Workshop on Worst-Case Execution Time Analysis (WCET 2010), volume 15 of OpenAccess Series in Informatics (OASIcs), pages 136–146, Brussels, Belgium, July 2010. Schloss Dagstuhl – Leibniz-Zentrum für Informatik. doi:10.4230/OASIcs.WCET.2010.136.

- 12 Syed Muhammad Zeeshan Iqbal, Yuchen Liang, and Hakan Grahn. Parmibench-an opensource benchmark for embedded multiprocessor systems. *IEEE Computer Architecture Letters*, 9(2):45–48, 2010.

- 13 C.G. Lee. UTDSP Benchmark Suite, July 2011. URL: http://www.eecg.toronto.edu/ ~corinna/DSP/infrastructure/UTDSP.html.

## 1:12 STR2RTS

- 14 Fadia Nemer, Hugues Cassé, Pascal Sainrat, Jean-Paul Bahsoun, and Marianne De Michiel. PapaBench: a Free Real-Time Benchmark. In 6th International Workshop on Worst-Case Execution Time Analysis (WCET'06), volume 4 of OpenAccess Series in Informatics (OASIcs). Schloss Dagstuhl – Leibniz-Zentrum für Informatik, 2006. doi:10.4230/OASIcs. WCET.2006.678.

- 15 Claire Pagetti, David Saussié, Romain Gratia, Eric Noulard, and Pierre Siron. The ROS-ACE Case Study: From Simulink Specification to Multi/Many-Core Execution. In 20th IEEE Real-Time and Embedded Technology and Applications Symposium, RTAS 2014, Berlin, Germany, April 15-17, 2014, pages 309–318, 2014.

- 16 Parasuite. URL: http://parasuite.inria.fr/.

- 17 Louis-Noël Pouchet. Polybench: The polyhedral benchmark suite, 2012. URL: http: //www.cs.ucla.edu/pouchet/software/polybench.

- 18 Wolfgang Puffitsch, Eric Noulard, and Claire Pagetti. Off-line mapping of multi-rate dependent task sets to many-core platforms. *Real-Time Systems*, 51(5):526–565, 2015.

- 19 Martin Schoeberl, Thomas B. Preusser, and Sascha Uhrig. The embedded java benchmark suite jembench. In Proceedings of the 8th International Workshop on Java Technologies for Real-Time and Embedded Systems, JTRES'10, pages 120–127, New York, NY, USA, 2010. ACM. doi:10.1145/1850771.1850789.

- 20 S. Stuijk, M.C.W. Geilen, and T. Basten. SDF<sup>3</sup>: SDF For Free. In Application of Concurrency to System Design, 6th International Conference, ACSD 2006, Proceedings, pages 276-278. IEEE Computer Society Press, Los Alamitos, CA, USA, June 2006. URL: http://www.es.ele.tue.nl/sdf3, doi:10.1109/ACSD.2006.23.

- 21 William Thies, Michal Karczmarek, and Saman Amarasinghe. Streamit: A language for streaming applications. In *Compiler Construction*, pages 179–196. Springer, 2002.

## Best Practice for Caching of Single-Path Code<sup>\*</sup>

Martin Schoeberl<sup>1</sup>, Bekim Cilku<sup>2</sup>, Daniel Prokesch<sup>3</sup>, and Peter Puschner<sup>4</sup>

- 1 Department of Applied Mathematics and Computer Science, Technical University of Denmark, Lyngby, Denmark masca@imm.dtu.dk

- $\mathbf{2}$ Institute of Computer Engineering, Vienna University of Technology, Vienna, Austria

- bekim@vmars.tuwien.ac.at

- Institute of Computer Engineering, Vienna University of Technology, Vienna, 3 Austria

- daniel@vmars.tuwien.ac.at

- 4 Institute of Computer Engineering, Vienna University of Technology, Vienna, Austria

peter@vmars.tuwien.ac.at

### — Abstract -

Single-path code has some unique properties that make it interesting to explore different caching and prefetching alternatives for the stream of instructions. In this paper, we explore different cache organizations and how they perform with single-path code.

**1998 ACM Subject Classification** C.3 Real-Time and Embedded Systems

Keywords and phrases single-path code, method cache, prefetching

Digital Object Identifier 10.4230/OASIcs.WCET.2017.2

#### 1 Introduction

Worst-case execution time (WCET) analysis is a non-trivial analysis problem. It becomes especially difficult with more complex processor architectures. A strategy to simplify WCET analysis is to write programs that have a constant execution time, i.e., the best-case and worst-case execution time are equal. In that case, we do not need to analyze the program, but can simply measure the execution time. Single-path code gives constant execution time [15].

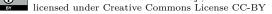

Single-path code is code that is structured so that there are no data dependent control flows. On an if/else condition both conditions are executed. However, to retain the program's semantics and data flow, all instructions are executed with a predicate. The compiler sets these predicates according to the original conditions of the branching code. When executing single-path code, instructions whose predicate evaluates to false do not update the processor state, i.e., they act as nop instructions. Loops always execute the maximum number of iterations (the so-called loop bound), which is a known number in a real-time context. Like the if/else case, the original loop condition is used to evaluate to a predicate and all instructions within loops are predicated.

The work presented in this paper was partially funded by the Danish Council for Independent Research Technology and Production Sciences under the project PREDICT (http://predict.compute.dtu.dk/), contract no. 4184-00127A. This paper was partially funded by the EU COST Action IC1202: Timing Analysis on Code Level (TACLe) and the European Union's 7th Framework Programme under grant agreement no. 288008: Time-predictable Multi-Core Architecture for Embedded Systems (T-CREST).

<sup>©</sup> Martin Schoeberl, Bekim Cilku, Daniel Prokesch, and Peter Puschner; licensed under Creative Commons License CC-BY

Editor: Jan Reineke; Article No. 2; pp. 2:1–2:12

<sup>17</sup>th International Workshop on Worst-Case Execution Time Analysis (WCET 2017).

**Open Access Series in Informatics**

OASICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

### 2:2 Best Practice for Caching of Single-Path Code

Single-path code can be manually coded or a compiler can translate *normal* code to single-path code. The translation of an *if/else* condition is also a common technique in compilers applied on small code fragments to avoid expensive branches. This is called if conversion [1].

The time-predictable execution of single-path code demands two features from a processor: (1) the processor needs to support predicates or a conditional move and (2) a predicated instruction shall have the same execution time irrespective of whether the predicate evaluates to true or false. Therefore, we explore single-path code on a processor that fulfills both conditions. Patmos is a processor that is designed especially for real-time systems [21]. Patmos contains features that shall make WCET analysis simpler, but also supports execution of single-path code with a predicated instruction set and constant execution time of instructions.

Patmos contains also a special instruction cache that caches full functions [4]. For historical reasons this cache is named method cache (it appeared first in a Java processor [18]). Cache misses can only occur at function calls or returns. Caching full functions has one drawback: code that is not executed is still loaded into the cache. However, as programs organized as single-path code execute all their instructions, this main drawback disappears. Therefore, our hypothesis is that the method cache is a good cache organization for single-path code.

This paper explores the method cache in the context of single-path code. We compare and evaluate the method cache against a standard instruction cache using the TACLeBench benchmarks [6]. Furthermore, we explore performance benefits of an extension of a standard instruction cache with a prefetcher that has been especially designed for single-path code.

The paper is organized in 6 sections: The following section presents related work. Section 3 provides background on single-path code generation and the time-predictable Patmos processor. Section 4 describes different options of caching for single-path code. Section 5 evaluates the different caching options on the Patmos processor and compares them. Section 6 concludes the paper.

## 2 Related Work

For real-time systems, caches are one of the main sources of temporal uncertainty. State-of-the-art cache analysis tools are using abstract interpretation for classifying cache accesses [12]. However, even if these approaches derive safe bounds, the precision of the results derived from the abstract models strongly vary depending on the cache architecture and replacement policy [9]. For example, an abstract model for the LRU replacement policy achieves better predictability than a model for FIFO or PLRU [17].

Another mechanism that aims at making caches more predictable is cache locking [14]. This technique loads memory contents into the cache and locks it to ensure that it will remain unchanged afterwards. The benefit of cache locking is that all accesses to the locked cache lines will always result into cache hits. The cache content can be locked entirely [7] or partially, it can be locked for the whole system lifetime (static locking) or it can be changed at runtime (dynamic locking) [5]. Although cache locking increases predictability, it reduces performance by restricting the temporal locality of the cache to a set of locked cache lines.

In contrast to conventional code, single-path conversion overcomes predictability issues by generating code that has only a single trace of execution. Thus, keeping traces of possible cache states is no more needed. Furthermore, the use of single-path code eliminates the necessity for cache locking.

## 3 Background

This paper builds on prior research work on single-path code and research on the timepredictable computer architecture developed for the T-CREST platform [19].

## 3.1 Single-path Code Generation

Puschner and Burns propose single-path code to simplify WCET analysis by avoiding datadependent control flow decisions [15]. The defining property of single-path code is that any execution follows a single instruction trace, independent from input data. This is achieved by conversion of control dependence to data dependence, with the use of predicated instructions. In code that is WCET analyzable, loops must be bounded. The compiler transforms inputdata dependent loops such that they iterate for a fixed number of times, which is the local loop bound [13].

The resulting single-path code may have a longer execution path, due to the serialization of otherwise alternative paths in the original program. Also, in some scenarios it is undesirable to always consume the computational resources required for the worst-case, e.g., in mixedcritical systems where slack time is used for non-critical tasks. Nonetheless, single-path code generation provides a constructive approach to time-predictable real-time code. On a "well-behaved" hardware platform, the execution time for single-path tasks is constant. In this ideal case, WCET analysis simplifies to measurement.

One requirement is that the instruction timing is independent of the instruction operands. Memory accesses introduce another source of variability in execution time. Though, the singlepath property makes the code easier to analyze with regards to instruction memory. Abstract interpretation based analysis becomes superfluous, there is no need for approximation. The known singleton instruction stream can be directly applied to a hardware model of the instruction cache (as in simulation). This knowledge is exploited to implement perfectly accurate prefetching schemes for instructions [2].

Data accesses are also subject to execution-time variability. Enforcing local availability of the required data during the task execution may alleviate the problem, e.g., by data cache locking or usage of a scratchpad memory. However, we restrict ourselves to the instruction cache in this paper.

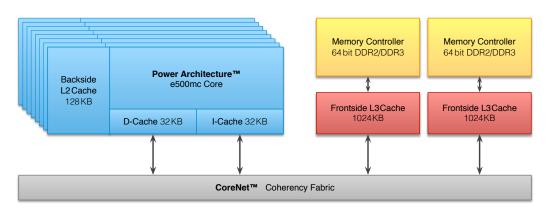

## 3.2 Patmos and the T-CREST Platform

We explore instruction caching options on the Patmos processor [21], which itself is part of the T-CREST multicore platform [19]. The T-CREST platform aims to build a processor, network-on-chip, and compiler toolchain [16] to simplify WCET analysis. We optimized all components to be time-predictable, even when average-case performance is reduced. AbsInt aiT [8] static WCET analyzer supports the Patmos processor. T-CREST also includes the research WCET analyzer platin [11].

Patmos is a RISC architecture supporting dual-issue instructions. To the best of our knowledge, Patmos is timing anomaly free. There is no timing dependency between any two instructions. Even all cache misses (instruction or data) happen in the same pipeline stage (the memory stage). Therefore, only a single cache miss can happen any clock cycle. Patmos uses special forms of instruction and data cache that shall simplify cache analysis. For instructions, Patmos has a method cache [4], which caches whole functions. Besides these special caches Patmos also supports a standard instruction cache, a standard data cache, and instruction and data scratchpad memories.

### 2:4 Best Practice for Caching of Single-Path Code

One issue with a method cache is that complete functions are loaded into the method cache, even when only part of it is executed. We attack this issue by splitting larger functions into smaller subfunctions [10]. However, with single-path code there is no code that is not executed. The processor executes all instructions of a called function. Therefore, a method cache may well fit for caching single-path code, especially when callee functions are not evicted by called functions.

We extended a standard instruction cache by a prefetching unit [3] to improve single-path execution time. The prefetcher uses the static "knowledge" of single-path code to anticipate the upcoming instructions and bring them into the cache before they are needed. Such a property allows the prefetcher to perform in time-predictable fashion without polluting the cache with unused instructions.

## 4 Caching of Single-Path Code

Single-path code is instruction-cache friendly as all instructions that are loaded into the cache are executed, except at the end of a function.

### 4.1 Standard Instruction Cache

A standard instruction cache is organized in cache blocks and can be configured as direct mapped cache or set associative cache. Some single-path code can benefit from a direct mapped instruction cache, especially when the cache is small [3]. We will evaluate direct mapped and set-associative instruction caches for single-path code.

## 4.2 Method Cache

The method cache is an instruction cache designed to simplify WCET analysis. The method cache caches full functions/methods. Therefore, a cache miss can only happen on a call or a return. All other instructions are guaranteed hits and cache analysis can ignore those. Method cache analysis only needs to consider functions and not individual instructions.

One disadvantage of the method cache is that instructions in a function that are not executed are still loaded on a cache miss. However, with single-path code all instructions of a function are always executed. Therefore, the method cache should perform well with single-path code.

### 4.3 Time-predictable Prefetcher with a Standard Cache

Prefetching hides large memory access latencies by loading instructions into the cache before they are needed. However, to take advantage of this improvement, the prefetcher needs to guess the right prefetch target and issue the request at the right time. Any wrong speculation on these two parameters can degrade the system performance.

The time-predictable prefetcher exploits properties of single-path code to anticipate the future instruction cache accesses with full accuracy and bring those instructions into the cache at the right moment [3]. For higher efficiency, the prefetcher implements an aggressive algorithm that prefetches every cache line of the code. Its direction is controlled through a *Reference Prediction Table* (RPT), which is an optimized projection of single-path code that captures the control-flow behavior of the code.

The entries of the RPT control the behavior of the prefetcher. They contain addresses at which the prefetcher should switch between sequential and non-sequential prefetching.

### M. Schoeberl, B. Cilku, D. Prokesch, and P. Puschner

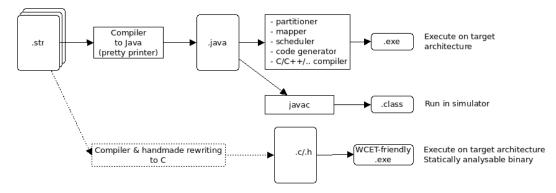

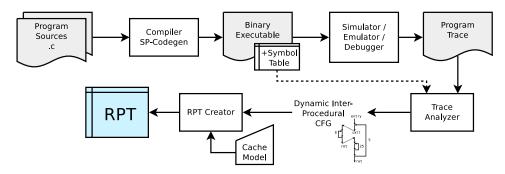

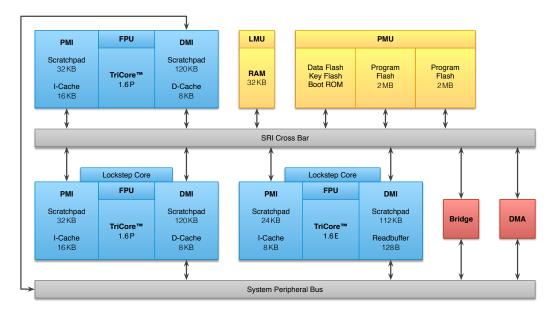

**Figure 1** Generation of the Reference Prediction Table (RPT).

Figure 1 shows the generation of the RPT. It begins with obtaining the execution trace of the single-path code. We use the Patmos simulator to export the program counter values during a program run. We extract the start addresses of the functions from the symbol table of the executable. The trace analyzer uses the trace and the start addresses to produce a dynamic control-flow graph of the single-path function, where nodes are addresses of single instructions. The trace analyzer identifies call sites, loops, loop nests, and loop iteration counts. The RPT creator then creates entries containing an address that shall trigger a change in the behavior of the prefetcher, a destination where to continue prefetching, and additional information depending on the entry type.

Generation of the RPT is based on a form of dynamic program analysis, without instrumentation of the original program. However, the extracted instruction trace is invariable regardless of the program inputs because of the single-path code. Also, in contrast to trace-based and profile-guided optimization, the analysis results are not directed back to the compiler. Instead, the execution is optimized by means of hardware in form of the specialized prefetcher.

## 5 Evaluation

We evaluate the program performance of single-path code with different caching methods. For the comparison, we use the Patmos processor. We configure Patmos for the Altera DE2-115 FPGA board, which means that the main memory is a 16-bit SRAM. This memory results in 21 clock cycles for a burst of 4 32-bit words to fill or spill a 16-byte cache line. All standard caches have the line size of the burst length, 16 bytes. We configure the instruction or method cache to be 8 KB large and the method cache to cache up to 16 functions. The data cache is 4 KB and the stack cache 2 KB. We use hardware simulation to get cycle accurate measurements.

For the evaluation, we use the TACLeBench benchmark collection [6] in version 1.9. We have added an attribute to the benchmarks' main function to avoid that it is inlined by the compiler. Otherwise we did not touch the source of TACLeBench. This main function is also the root function for the single-path code generation. We measure the execution time of the whole program, including initialization and result comparison code, in clock cycles.

We used a subset of the benchmarks. The variation of the execution time of the benchmarks is high, i.e., between hundreds and a billion clock cycles. For practical reasons, we did not use the long running benchmarks, as cycle accurate hardware simulation is time consuming.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> The simulation of the remaining benchmarks, just for a single cache size configuration, still takes 6–8 hours on a contemporary notebook.

### 2:6 Best Practice for Caching of Single-Path Code

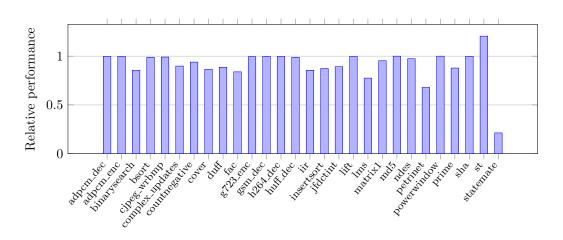

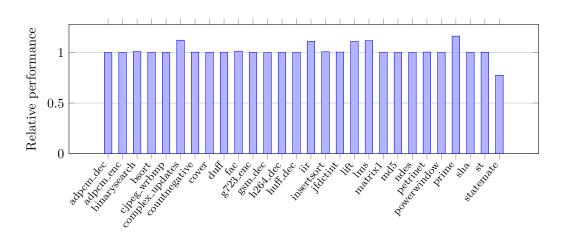

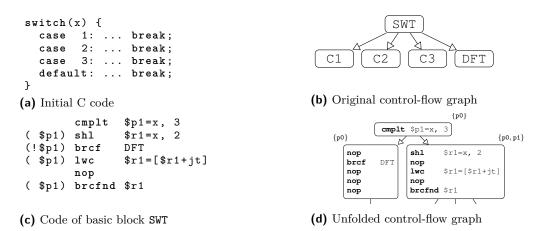

**Figure 2** Relative average-case performance comparing the method cache with a standard cache on normal programs.

However, a large execution time does not necessarily mean that those benchmarks would have a larger memory foot print. Furthermore, we dropped benchmarks where we cannot generate single-path code, e.g., recursive benchmarks. Also, we removed two outliers (ludcmp and minver) as their results showed improvements of factors 3 to 4 for the method cache compared to a standard instruction cache.

All the following figures show measured performance improvements, where a bigger number means a better result. The figures show relative performance as one execution time scaled by the other execution time. That means a number larger than 1 is an improvement, and a number less than 1 is a regression. E.g., when comparing the method cache with the standard cache, the figure shows how much better (or worse) the configuration of the method cache is compared with the standard cache. For this example, the relation is the execution time of the benchmark with the standard cache divided by the execution time of the benchmark with the method cache (as a shorter execution time is better).

## 5.1 Baseline

As a baseline, we show the performance difference between using a method cache and a direct mapped instruction cache on normal compiled code. Figure 2 shows the execution time relation between those two configurations (normalized to the execution time with the standard cache). The geometric mean of the comparison is 0.88, which means that on average the configuration with the direct mapped instruction cache performs better. Those measurements are average case measurements and cannot be an indication of WCET analysis bounds. In these average case measurements, we see that some benchmarks perform equally for the two cache configurations. We assume those cases are when the benchmark fits entirely into the cache. Several benchmarks perform better with a normal instruction cache than with the method cache. However, this is an average case measurement and the method cache was designed to simplify WCET analysis.

## 5.2 Single-Path Comparison and Prefetching

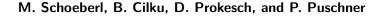

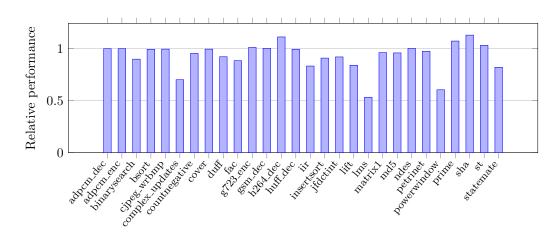

Figure 3 shows the performance comparison between a method cache and a standard cache with single-path generated code. The figure is now more diverse than the average-case figure.

**Figure 3** Relative single-path performance comparing the method cache with a standard cache.

**Figure 4** Relative single-path performance comparing the method cache with a prefetching cache.

Some benchmarks gain and some lose when using a method cache. There is no clear winner. The geometric mean of the comparison is 0.96, which means that on average the standard cache configuration performs slightly better.

Figure 4 show the performance comparison between a method cache and an instruction cache that includes the prefetching unit. The results are similar to the results in Figure 3. Some benchmarks gain a little bit with the prefetching unit. The geometric mean of the comparison is 0.94. We assume that most benchmarks are almost fitting into the cache and leaving not enough room for improvement by prefetching. It has been shown that smaller caches benefit most from the prefetcher [3].

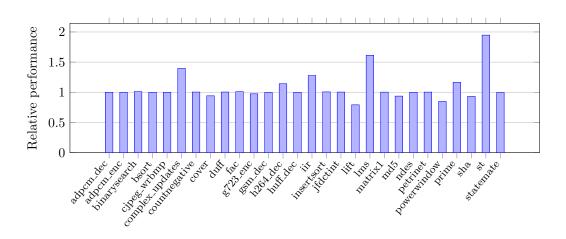

## 5.3 Associativity

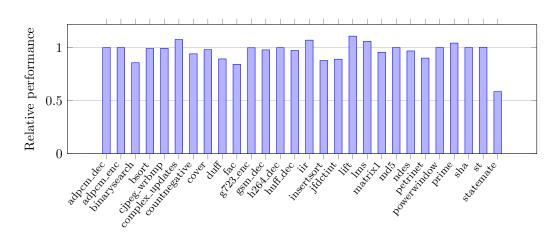

Figure 5 shows the comparison of a 2-way cache with LRU replacement with a direct mapped instruction cache. Originally we assumed that a direct mapped cache is a better fit for single-path code as is avoids cache thrashing on loops that are larger than the cache. However, we see in the figure that some benchmarks benefit from a higher associativity. Only **statemate** performs better with a direct mapped cache. Therefore, we deduct that the 4 KB of one way is large enough for the larger loops in the benchmarks. The geometric mean of the comparison

### 2:8 Best Practice for Caching of Single-Path Code

**Figure 5** Relative single-path performance comparing a 2-way cache with a direct mapped cache.

**Figure 6** Benchmark dynamic sizes (instruction memory footprint).

is 1.014, which means that on average the configuration with the 2-way instruction cache performs slightly better than the configuration with the direct mapped cache.

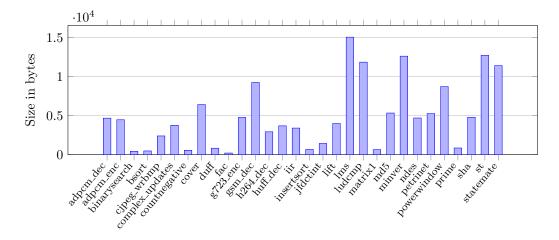

## 5.4 Benchmark Sizes

To better understand the benchmark results, we measure the instruction memory footprint of the benchmarks. We collect actual runtime data of which code is executed. We trace the execution of a benchmark with the Patmos simulator and collect which functions are executed. We extract the function sizes from the executable. As single-path code executes the whole function, we simply add all sizes of the executed functions to retrieve the instruction memory footprint. We exclude startup and exit code.

Figure 6 shows the memory footprint of the benchmarks. We can see three typical sizes of benchmarks: (1) very small benchmarks, such as **binarysearch** or **duff** where the memory footprint is less than 1 KB, (2) medium sized benchmarks with a memory footprint of 4–5 KB, and (3) larger benchmarks with a memory footprint of around 10 KB. The largest benchmark is **lms** with 14.7 KB. These numbers do not include any startup or exit code executed, which by itself is 7048 bytes. That means for the small benchmarks the startup and exit code dominates the memory footprint.

### M. Schoeberl, B. Cilku, D. Prokesch, and P. Puschner

**Figure 7** Relative single-path performance comparing the method cache with a standard cache (2 KB size).

With our standard configuration of 8 KB instruction cache, 23 out of the 30 benchmarks will fit into the cache (excluding startup and exit code). This means that many of the TACLeBench benchmarks are too small for the evaluation of different instruction caches. Therefore, we explore artificial small caches in the following subsection.

## 5.5 Small Caches

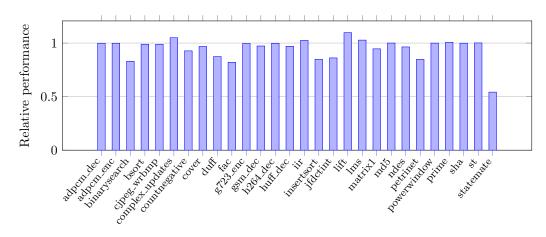

For further experiments we reduce the size of the instruction and method cache to just 2 KB, a very small size for current embedded processors. Figure 7 compares the method cache with the direct mapped instruction cache. For this evaluation we leave the compiler parameter preferred subfunction size at the default value of 256. The geometric mean of the comparison is 0.92, which means that on average a direct mapped instruction cache is a slightly better solution for small caches.

Figure 8 compares a 2-way cache with LRU replacement with a direct mapped instruction cache. Compared to Figure 5 we see different benchmarks benefitting from associativity. Furthermore, with the larger cache only a single benchmark (statemate) performed worse with the 2-way cache. For the small configuration, several benchmarks perform worse with a 2-way set associative cache. Therefore, for small caches there is no clear winner when comparing a direct mapped and a 2-way set associative instruction cache. The geometric mean of the comparison is 1.05, which means that on average a 2-way set associative instruction cache is a slightly better solution than a direct mapped instruction cache for small cache sizes.

## 5.6 Discussion

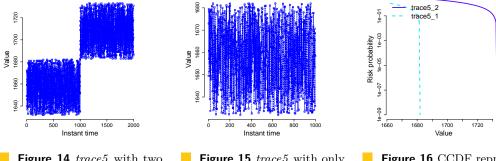

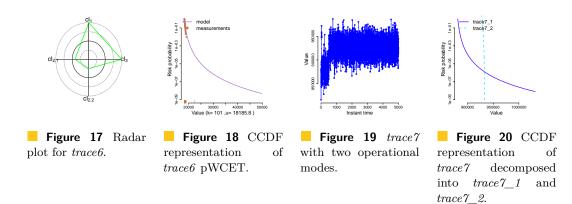

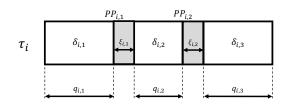

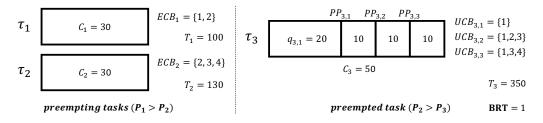

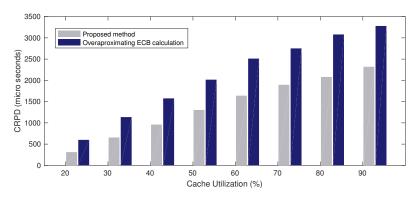

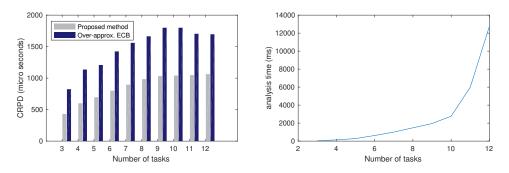

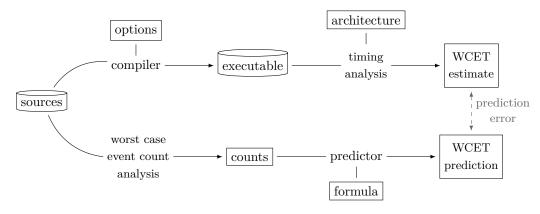

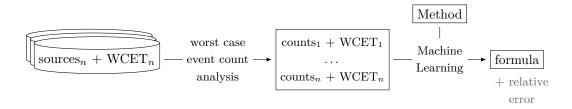

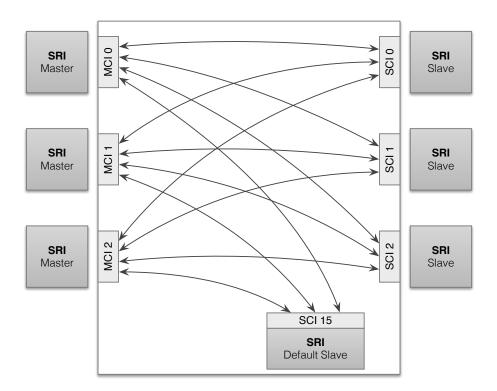

Single-path code has different characteristics than normal code. We see some of the different characteristics when comparing different caching methods. The method cache, which works not so well in the average-case, is a better fit when using single-path code. Prefetching with a standard cache provides some benefit.