# Third Workshop on Next Generation Real-Time Embedded Systems

NG-RES 2022, June 22, 2022, Budapest, Hungary

Edited by Marko Bertogna Federico Terraneo Federico Reghenzani

www.dagstuhl.de/oasics

Editors

Marko Bertogna Università di Modena e Reggio Emilia, Italy marko.bertogna@unimore.it

Federico Terraneo Politecnico di Milano, Italy federico.terraneo@polimi.it

Federico Reghenzani Politecnico di Milano, Italy federico.reghenzani@polimi.it

ACM Classification 2012 Computer systems organization  $\rightarrow$  Real-time systems; Computer systems organization  $\rightarrow$  Embedded and cyber-physical systems

# ISBN 978-3-95977-221-1

Published online and open access by

Schloss Dagstuhl – Leibniz-Zentrum für Informatik GmbH, Dagstuhl Publishing, Saarbrücken/Wadern, Germany. Online available at https://www.dagstuhl.de/dagpub/978-3-95977-221-1.

Publication date June, 2022

Bibliographic information published by the Deutsche Nationalbibliothek The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at https://portal.dnb.de.

#### License

This work is licensed under a Creative Commons Attribution 4.0 International license (CC-BY 4.0): https://creativecommons.org/licenses/by/4.0/legalcode. In brief, this license authorizes each and everybody to share (to copy, distribute and transmit) the work

under the following conditions, without impairing or restricting the authors' moral rights: Attribution: The work must be attributed to its authors.

The copyright is retained by the corresponding authors.

Digital Object Identifier: 10.4230/OASIcs.NG-RES.2022.0

ISBN 978-3-95977-221-1

ISSN 1868-8969

https://www.dagstuhl.de/oasics

# OASIcs - OpenAccess Series in Informatics

OASIcs is a series of high-quality conference proceedings across all fields in informatics. OASIcs volumes are published according to the principle of Open Access, i.e., they are available online and free of charge.

#### Editorial Board

- Daniel Cremers (TU München, Germany)

- Barbara Hammer (Universität Bielefeld, Germany)

- Marc Langheinrich (Università della Svizzera Italiana Lugano, Switzerland)

- Dorothea Wagner (*Editor-in-Chief*, Karlsruher Institut für Technologie, Germany)

#### ISSN 1868-8969

https://www.dagstuhl.de/oasics

# **Contents**

| Preface                                                                                                       |            |

|---------------------------------------------------------------------------------------------------------------|------------|

| Marko Bertogna, Federico Terraneo, and Federico Reghenzani                                                    | 0:vii      |

| Program Committee                                                                                             |            |

|                                                                                                               | 0:ix       |

| Invited Paper                                                                                                 |            |

| Can We Trust AI-Powered Real-Time Embedded Systems?                                                           |            |

| Giorgio Buttazzo                                                                                              | 1:1-1:14   |

| Regular Papers                                                                                                |            |

| Multi-Requirement Enforcement of Non-Functional Properties on MPSoCs Using<br>Enforcement FSMs – A Case Study |            |

| Khalil Esper, Stefan Wildermann, and Jürgen Teich                                                             | 2:1-2:13   |

| Overlapping-Horizon MPC: A Novel Approach to Computational Constraints in<br>Real-Time Predictive Control     |            |

| Alberto Leva, Simone Formentin, and Silvano Seva                                                              | 3:1 - 3:10 |

| Ahead-Of-Real-Time (ART): A Methodology for Static Reduction of Worst-Case Execution Time                     |            |

| $Daniele \ Cattaneo, \ Gabriele \ Magnani, \ Stefano \ Cherubin, \ and \ Giovanni \ Agosta \ \ldots$          | 4:1-4:10   |

# Preface

This volume collects the papers presented at the third edition of the Workshop on Next Generation Real-Time Embedded Systems (NG-RES 2022). The workshop is co-located with the 2022 edition of the HiPEAC conference and was held on June 22, 2022 in Budapest, Hungary.

The traditional concept of embedded systems is constantly evolving to address the requirements of the modern world. Cyber-physical systems, networked control systems and Industry 4.0 are introducing an increasing need for interconnectivity. A steadily increasing algorithmic complexity of embedded software is fueling the adoption of multicore and heterogeneous architectures. As a consequence, meeting real-time requirements is now more challenging than ever. The NG-RES workshop focuses on real-time embedded systems, with particular emphasis on the distributed and parallel aspects. The workshop is a venue for both the networking and multicore real-time communities aiming at cross-fertilization and multi-disciplinary approaches to the design of embedded systems. The NG-RES workshop focuses on real-time embedded systems, with particular emphasis on the distributed and parallel aspects. The workshop is a venue for both the networking and multicore real-time communities aiming at cross-fertilization and multi-disciplinary approaches to the design of embedded systems. The design of both the networking and multicore real-time communities aiming at cross-fertilization and multi-disciplinary approaches to the design of embedded systems.

The scope of the NG-RES workshop include the following topics:

- Programming models, paradigms and frameworks for real-time computation on parallel and heterogeneous architectures

- Networking protocols and services (e.g., clock synchronization) for distributed real-time embedded systems

- Scheduling and schedulability analysis for distributed and/or parallel real-time systems

- System-level sofware and technologies (e.g. RTOSs, hypervisors, separation kernels, virtualization) for parallel and heterogenous architectures

- Application of formal methods to distributed and/or parallel real-time systems

- Compiler-assisted solutions for distributed and/or parallel real-time systems

- Middlewares for distributed and/or parallel real-time systems

In this third edition of the workshop three regular papers were accepted, each of which receiving between two and three peer reviews. In addition, we are glad to have an invited paper by Giorgio Buttazzo titled "Can We Trust AI-Powered Real-Time Embedded Systems?". We would like to thank the authors of the NG-RES 2022 papers, the members of our program committee, our publisher Schloss Dagstuhl as well as the HiPEAC organizers for contributing to the success of this workshop.

Marko Bertogna, Federico Terraneo, and Federico Reghenzani

# Program Committee

#### **General Chair**

Marko Bertogna, Università di Modena e Reggio Emilia, Italy

#### **Program Chair**

- Federico Terraneo, Politecnico di Milano, Italy

- Federico Reghenzani, Politecnico di Milano, Italy

#### **Program Committee**

- Alberto Leva, Politecnico di Milano, Italy

- Ashik Ahmed Bhuiyan, University of Central Florida, United States

- Benny K. Akesson, TNO, Netherlands

- Christine Rochange, Institut de Recherche en Informatique de Toulouse, France

- Filip Markovic, Mälardalen University, Sweden

- Jaume Abella Ferrer, Barcelona Supercomputing Center, Spain

- Lucia Lo Bello, University of Catania, Italy

- Luís Almeida, Universidade do Porto, Portugal

- Jürgen Teich, Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany

- Marco Solieri, Università di Modena e Reggio Emilia, Italy

- Roberto Cavicchioli, Università di Modena e Reggio Emilia, Italy

# Can We Trust AI-Powered Real-Time Embedded Systems?

# Giorgio Buttazzo 🖂

Department of Excellence in Robotics & AI, Scuola Superiore Sant'Anna, Pisa, Italy

#### — Abstract

The excellent performance of deep neural networks and machine learning algorithms is pushing the industry to adopt such a technology in several application domains, including safety-critical ones, as self-driving vehicles, autonomous robots, and diagnosis support systems for medical applications. However, most of the AI methodologies available today have not been designed to work in safety-critical environments and several issues need to be solved, at different architecture levels, to make them trustworthy. This paper presents some of the major problems existing today in AI-powered embedded systems, highlighting possible solutions and research directions to support them, increasing their security, safety, and time predictability.

2012 ACM Subject Classification Computer systems organization

Keywords and phrases Real-Time Systems, Heterogeneous architectures, Trustworthy AI, Hypervisors, Deep learning, Adversarial attacks, FPGA acceleration, Mixed criticality systems

Digital Object Identifier 10.4230/OASIcs.NG-RES.2022.1

Category Invited Paper

# 1 Introduction

Embedded computing platforms are becoming more complex every day to manage the increasing computational load generated by emerging applications, as autonomous vehicles (cars, trains, drones, aircrafts), advance robotic systems, intelligent appliances, and so on. Such systems are equipped with a variety of sensors that produce a large amount of data, hence demanding for real-time processing and high-performance computing. To provide the required computational power, computer architectures are evolving towards heterogeneous platforms that integrate on the same board, or even on the same chip, multicore processors of different types, field programmable gate arrays (FPGAs), general purpose graphics processing units (GPGPUs), and special co-processors optimized for executing operations on tensors, as tensor processing units (TPUs).

Although new tools and libraries are becoming available every year, developing safetycritical applications on top of such heterogeneous platforms, while providing the required guarantees, is quite difficult due to a number of non-trivial problems. The following list presents just a few of such problems, related to the use of artificial intelligence (AI) in safety-critical applications with real-time constraints.

- The interaction among the various components through the shared resources available on the computing platform (as buses, memories, and I/O devices) generates a significant amount of interference, introducing large and unpredictable delays on the computational activities. Such a large variability in responding to external events makes it is very difficult to provide timing guarantees on the application behavior. This is also a serious problem for the certification of safety-critical software components.

- Programming modern heterogeneous platforms requires a deep knowledge of low-level details of the architecture, which prolongs the developing and testing times.

© Giorgio Buttazzo;

licensed under Creative Commons License CC-BY 4.0

Third Workshop on Next Generation Real-Time Embedded Systems (NG-RES 2022).

Editors: Marko Bertogna, Federico Terraneo, and Federico Reghenzani; Article No. 1; pp. 1:1–1:14

OpenAccess Series in Informatics OASICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

# 1:2 Can We Trust AI-Powered Real-Time Embedded Systems?

- Distributing the computational activities in an optimal way between hardware accelerators and processors is not trivial, but it can make a huge difference in the overall system performance, as well as in satisfying the real-time application constraints.

- Deep neural networks (DNNs) are commonly developed and inferred by means of state-of-the-art frameworks (e.g., Tensorflow, Caffe, and PyTorch), which greatly simplify the implementation of new models. Unfortunately, however, none of the current frameworks is specifically optimized to be used in safety-critical environments, nor capable of providing bounded response times. This prevents their use in real-time applications like autonomous driving, where DNNs should have a highly predictable behavior, not only in the functional domain, but also in the time domain, responding within specific deadlines.

- The use of deep learning algorithms and the related frameworks increases the software attack surface, posing serious security issues for the overall system. This problem is exacerbated by the fact that such frameworks usually run on top of rich operating systems, as Linux, which are more vulnerable to cyber attacks.

- In spite of their excellent capabilities in perception tasks, deep neural networks have been shown to be prone to adversarial attacks, i.e., malicious inputs with imperceptible perturbations that force a neural network to produce a wrong output with a high confidence score.

- Similar threats derive from inputs that significantly differ from the distribution of the training set. Predicting the behavior of a neural network on such inputs is not easy and, in some cases, the network could also respond with a wrong output with a high confidence score.

- Finally, since the behavior of a neural network is not explicitly programmed, but encoded in a huge number of parameters, interpreting the output of a neural model and deciding whether its prediction can be trusted is a challenging task.

To address the issues described above, a lot of research is being devoted to support the development of AI-powered applications on top of heterogeneous platforms for safety-critical real-time systems.

The remainder of the paper is organized as follows: Section 2 discusses the problems and preliminary solutions related to architecture issues; Section 3 presents problems and promising solutions related to security issues; Section 4 describes the major threats caused by the use of AI algorithms and some solutions aimed at mitigating them; Section 5 proposes an architectural approach to address all the issues discussed above; and Section 6 states the conclusions and outlines some promising research lines.

# 2 Architecture issues

To be used in real time, the inference of modern DNN models requires hardware acceleration. This can be achieved by exploiting modern heterogeneous computing platforms equipped by GPUs or programmable hardware, as FPGA. This section discusses the main problems related to such computing platforms and presents existing solutions to them.

# 2.1 General platform issues

To cope with the different computational requirements of real-time applications, modern heterogeneous computing platforms integrate different processing elements, as multi-core processors of different types, general purpose GPGPUs, FPGAs, and tensor processing units.

#### G. Buttazzo

The concurrent accesses to shared devices existing on such architectures, as buses, memory controllers, and high-level caches, create a significant interference on the computations, introducing long and variable delays in application tasks.

For instance, Cavicchioli et al. [12] observed significant and variable delays when using GPU acceleration on heterogeneous embedded platforms due to the contention occurring on shared memory, especially for memory-intensive GPU tasks. Restuccia et al. [29] identified some anomalous situations that can arise in an AXI bus arbiter in FPGA-based SoC and proposed a reservation mechanism to prevent this phenomenon and restore fairness during bus transactions.

A timing analysis has also been proposed [28] to bound the execution of periodicallyinvoked hardware accelerators in nominal conditions. This analysis can be used to configure a latency-free hardware module named AXI Stall Monitor (ASM) to detect and safely solve possible stalls during AXI bus transactions. Efforts have also been devoted to analytically bound the delay experienced by AXI bus transactions issued by hardware accelerators on FPGA [30].

Hardware acceleration typically involves memory-intensive computations. Therefore, an accurate control of the memory traffic is crucial to achieve predictability in the execution of HW-tasks.

Pagani et al. [26] proposed a bandwidth reservation mechanism for AXI-based transactions on FPGAs able to control the bus traffic generated by hardware accelerators. The mechanism, named Memory Budget and Protection Unit (MBPU), aims at "shielding" hardware accelerators from excessive or unpredictable memory interference. MBPUs are installed between AXI master ports and the interconnect, enforcing a given budget of memory transactions within a periodic interval of time. Budgets are recharged in a periodic fashion and are configurable from the CPU via memory-mapped registers. MBPUs also protect the system from unrestricted accesses to memory by HW-tasks: this is accomplished by masking the accesses that fall outside a set of configurable memory address spaces.

#### 2.2 GPU-related issues

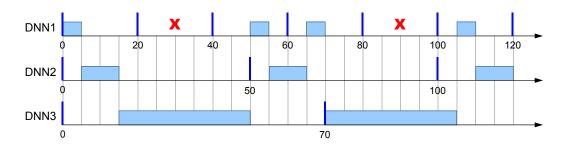

Today, the most common way for accelerating DNNs is by executing them on a GPU-based platform. This solution has two main advantages: (i) the response time can be reduced by two orders of magnitude and (ii) the development is supported by standard frameworks. However, GPUs also have disadvantages. First, they are closed systems and multiple tasks are scheduled in a non preemptive fashion. This means that, if the system includes multiple neural networks with different complexity and periodicity requirements, those with shorter periods will be more likely to experience longer delays and higher response time variability. An example of non-preemptive schedule of three DNNs with different execution times and periods is illustrated in Figure 1.

Notice that, in this example, the total GPU utilization is less than one (U = 0.95), but DDN1 is forced to skip the second and the fifth execution instance, because it cannot preempt the execution of DNN3.

To solve this problem, Capodieci et al. [9], in collaboration with NVIDIA, proposed to modify the GPU internal scheduler with a preemptive scheduler based on Earliest Deadline First (EDF) [18], also providing bandwidth isolation by means of a Constant Bandwidth Server (CBS) [3]. Unfortunately, however, this solution is not yet available on commercial NVIDIA GPU platforms.

Other problems with GPU acceleration are due to the high power consumption and their significant weight and encumbrance, which prevent their usage in small embedded systems, as unmanned aerial vehicles (UAVs).

**Figure 1** Example of non-preemptive schedule of three DNNs with different execution times and periods. As clear from the figure, DNN1 experiences longer and variable delays.

# 2.3 FPGA-related issues

An interesting alternative to GPUs for accelerating AI algorithms is provided by FPGAs. They are integrated circuits designed to be configured after manufacturing for implementing arbitrary logic functions in hardware. As such, they exhibit a highly predictable behavior in terms of execution times. In addition, they consume much less power with respect to GPUs and existing commercial platforms are characterized by lower weight, encumbrance, and cost. Hence, they represent an ideal solution for being used on battery-operated embedded systems with size, weight, power and cost (SWaP-C) constraints, as space robots, satellites, and UAVs.

Nevertheless, FPGAs have other problems when used as DNNs accelerators:

- No floating point unit (FPU) is available on the chip, unless it is explicitly programmed by the user, but consuming a significant fraction of the available fabric.

- Programming FPGAs is quite more difficult than programming CPUs or GPUs, and efficient coding requires a deep knowledge of low-level architecture details.

- The frameworks available today for developing AI applications on FPGA-based platforms are less rich and flexible than those available for GPUs, and the same is true for related libraries and tools.

- The overall FPGA area available in medium size SoCs could be insufficient to host more than one DNN, or even a single large DNN.

To overcome the problems outlined above, a lot of research has been carried out in the recent years.

The absence of an FPU is overcome by performing a preliminary parameter quantization to convert floating point numbers into integers with *n*-bit precision. Several quantization methods have been proposed in the literature [17], including symmetrical, asymmetrical, non-uniform, and statistical. An extreme quantization converts weights into binary numbers using the sign function. Courbariaux, Bengio, and David [14] have shown that a binarized DNN can achieve 98.8% accuracy in classifying the handwritten digits of the MNIST dataset. Other optimization steps (e.g., network pruning and layer fusion) can also be performed, both on GPUs and FPGAs, to reduce the computation time and the memory footprint of trained DNNs while minimizing the loss in accuracy.

To overcome the limitation of the FPGA area, Biondi et al. [6] proposed a programming framework, called FRED<sup>1</sup>, to support the design, development, and execution of predictable software on FPGAs. FRED exploits dynamic partial reconfiguration and recurrent execution

<sup>&</sup>lt;sup>1</sup> See details on http://fred.santannapisa.it.

to virtualize the FPGA area, thus enabling the user to allocate a larger number of hardware accelerators than those that could otherwise be fit into the physical fabric. FRED also integrates a tool for automated floorplanning [33] and a set of runtime mechanisms to enhance predictability by scheduling hardware resources and regulating bus/memory contentions [29].

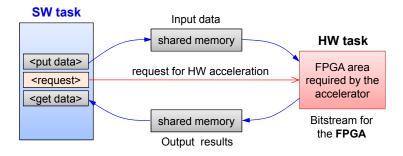

An application targeted by FRED consists of a set of software tasks (SW-tasks) running on the CPU cores that can periodically invoke the execution of hardware accelerators (HWtasks) to be dynamically programmed on the FPGA. The communication scheme adopted between SW-tasks and HW-tasks is illustrated in Figure 2.

**Figure 2** Communication scheme adopted between SW-tasks and HW-tasks in FRED.

The FPGA virtualization is achieved through a timesharing mechanism that replaces inactive accelerators (i.e., those that finished their computation and are waiting for the next activation) with active ones. In this way, the total number of HW-tasks that can run on the FPGA can be much higher than the number of HW-tasks that would statically fit in the physical area available on the fabric. Hence, this mechanism virtualizes the FPGA by creating a virtual area much larger than the physical one. The resulting approach is similar to multitasking, where tasks continuously change their context, or a virtual memory mechanism, where memory pages are swapped between hard disk and dynamic memory.

Thanks to a set of design choices and a proper scheduling infrastructure, resource contention delays experienced by tasks running under FRED are bounded and predictable, and hence they can be estimated to verify the system schedulability.

A full support for FRED has been developed under both FreeRTOS and Linux [25, 24]. The Linux support comes with a user-space daemon and a set of custom kernel drivers to handle the processor configuration port (PCAP) and the shared-memory communication buffers between CPUs and FPGA. A preemptable reconfiguration interface has also been developed by Rossi et al. [31] to achieve a finer control in scheduling the reconfiguration requests and a better control on the reconfiguration delays incurred by HW-tasks.

#### 2.4 Framework issues

DNNs are commonly developed and inferred by means of state-of-the-art frameworks, as Tensorflow, Caffe, and PyTorch. Unfortunately, such frameworks are not optimized for being used in real-time applications and they are not supported by commercial real-time operating systems, as VxWorks and QNX. As a consequence, DNN tasks may be subject to a variable interference.

Casini et al. [10] addressed this problem by modifying the internal scheduler of the TensorFlow framework and adapting it for the SCHED\_DEADLINE scheduling class of Linux. Extensive experiments demonstrated the effectiveness of the approach, showing a significant reduction of both average and longest-observed response times of TensorFlow tasks.

#### 1:6 Can We Trust AI-Powered Real-Time Embedded Systems?

Recently, Restuccia and Biondi [27] proposed a set of techniques for accelerating DNNs on FPGA-based platforms with a highly predictable timing behavior under the Vitis AI frameworks by Xilinx. In Vitis AI, the execution of the DNN layers relies on the deep learning processing unit (DPU) core, a hardware accelerator optimized for the execution of convolutional DNNs. Based on an extensive profiling campaign conducted on the Xilinx Zynq Ultrascale+ platform, they proposed an execution model for the DPU employed to derive a response time analysis for guaranteeing real-time applications constraints.

# **3** Security issues

Safety-critical systems that make use of AI algorithms consist of several components with different complexity and requirements.

Consider for example a self-driving car. The functions responsible for steering, throttle modulation, braking, and engine control are highly critical and must satisfy stringent requirements in terms of safety, security, and real-time behavior. As such, they need to be managed by a real-time operating system, that must be certified to guarantee the required safety integrity levels.

On the other hand, high-level functions related to sensory perception, object tracking, and vehicle localization, which heavily rely on AI algorithms, need to be executed on a rich operating system (e.g., Linux) to exploit all the available device drivers, libraries, and development frameworks required for such complex computations. These components are far from being certified and offer a large software surface for cyber attacks.

In 2015, two hackers, Charlie Miller and Chris Valasek, discovered a vulnerability in the Jeep Cherokee, which they exploited to remotely access the vehicle and gain physical control, including steering, braking, turning on the wipers, blasting the radio, and finally, killing the engine to bring the vehicle to a complete stop [15]. They wrote a long paper [19] where they explain how they accessed the CAN bus through the infotainment system, detailing the full attack chain.

Although cyber attacks to non critical components accessible by a wireless network cannot be avoided completely, the security of a system can greatly be enhanced by preventing such attacks from spreading to more critical components. This can be achieved by *isolating* software components with different level of criticality into different execution domains, through the use of a hypervisor.

# 3.1 Hypervisor-based architecture

A hypervisor is a software layer above the hardware platform able to create and manage multiple execution domains, each hosting a virtual machine with its own operating system.

An example of a hypervisor-based architecture for safety-critical embedded systems is the one proposed by the SPHERE project [7], which supports the creation of multiple virtual machines on the same computing platform, providing both time/memory isolation, security, real-time communication channels, and I/O virtualization to allow different virtual machines to shared the peripheral devices.

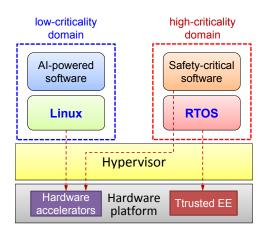

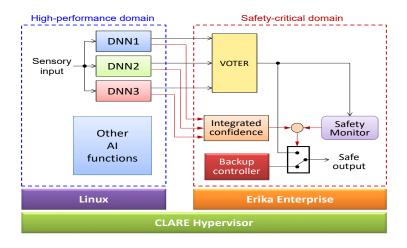

Figure 3 shows an example of a hypervisor managing two execution domains with different levels of criticality. One domain hosts a virtual machine running all safety-critical functions on a real-time operating system (RTOS), while the other domain hosts another virtual machine running AI-powered software on the Linux operating system. Such an architecture has been

successfully implemented and tested on a number of AI-powered control applications using CLARE [2], a novel hypervisor purposely designed to support mixed-criticality real-time systems exploiting AI hardware acceleration in heterogeneous embedded platforms.

# 3.2 CLARE hypervisor

The CLARE hypervisor is a novel bare-metal (type-1) hypervisor at the core of the CLARE software stack [2]. It integrates cutting-edge mechanisms to host safe, secure, and time-predictable virtual machines that can execute in isolation upon the same hardware platform. CLARE hypervisor follows a fully-static approach with off-line configurations and optimization to allocate the onboard resources to virtual machines. It has been designed to support modern heterogeneous platforms, such as GPGPU- and FPGA-based SoC, to better exploit and control their computational resources. In particular, it provides a number of real-time and security features that make it suitable for safety-critical systems, such as

- Improved key management and attack detection under control flow integrity by pointer authentication code [16].

- Hardware-based isolation exploiting the ARM TrustZone technology to perform key management and provide attack detection and recovery strategies.

- Virtualization of trusted execution environments leveraging ARM TrustZone [13].

- Protection mechanisms at the hypervisor level to control temporal and spatial interference among domains, also preventing side-channel attacks [20].

- I/O device virtualization and I/O related memory contention control, with related latency analysis [11].

- FPGA virtualization to allow multiple domains to exploit hardware accelerators in isolation.

# 4 AI related issues

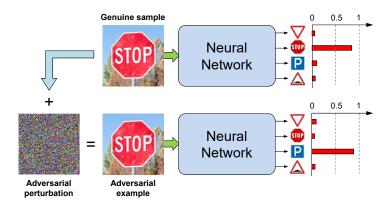

Deep neural networks have shown an impressive performance in several recognition tasks, but their suitability for mission-critical applications has been questioned by Szegedy et al. [35] and many other authors [34], who showed that imperceptible perturbations added to an input sample can fool a neural network in perceiving objects that are not present in the input. Such perturbed inputs are called adversarial examples (AEs) and represent a serious

#### 1:8 Can We Trust AI-Powered Real-Time Embedded Systems?

**Figure 4** Example in which a neural network is able to correctly classify a genuine image of a stop sign (top). However, the same image can be modified by adding an adversarial perturbation, so that it is classified as a parking sign with a high confidence score (bottom).

threat for the security of AI-based systems. An example of adversarial image is shown in Figure 4, where the picture of a stop sign is perturbed in such a way that it is perceived by the network as a parking sign with a high confidence score.

Although a significant effort has been spent to develop defense methods against adversarial examples [5], the problem remains open and challenging, since these attacks violate the fundamental stationarity assumption of learning algorithms, i.e., that training and testing data are drawn from the same distribution.

The trustworthiness of DNNs is also threatened by genuine inputs characterized by a distribution that is quite different from that of the training samples. Such inputs are referred to as *out-of-distribution* (OoD) samples. Two examples of OoD images are shown in Figure 5.

**Figure 5** Two examples of OoD images that could cause a deep neural network to produce a wrong output.

Considering that the prediction score of a DNN can be high in the presence on both AEs and OoD samples, the output score of the best classified class cannot be considered as an indication of the prediction confidence of the model.

Several methods have been proposed in the literature to detect AEs and OoD samples. Two of these methods are presented below with more details.

# 4.1 Detection by input transformations

One method for detecting AEs relies on the fact that DNN models are usually robust to certain types of input transformations (e.g., translation, rotation, scaling, blurring, noise addition, etc.). This means that, if a genuine image is correctly recognized by a DNN, the

#### G. Buttazzo

prediction score reduces only slightly when the same image is translated, rotated, or modified with one the mentioned transformations. However, the same is not true for most AEs and it has been observed that they result to be more sensitive to input transformations, which cause a much higher degradation in the prediction score.

This property of AEs has been exploited by some authors [37] to detect whether an input x is adversarial or genuine. If y = f(x) is the top class score produced by the DNN on input x and  $y_T = f(T(x))$  is the score produced on the transformed input T(x), a simple detection method is to consider x to be adversarial if the difference  $y - y_T$  is higher than a given threshold  $\tau$ .

Unfortunately, it is possible to generate adversarial examples that are robust to input transformations. To cope with this case, Nesti et al. [22] proposed a new method, called *defense perturbation*, capable of detecting AEs that are robust to input transformations. The defense perturbation is generated by a proper optimization process capable of making robust AEs sensitive again to input transformations. Furthermore, the paper introduces multi-network AEs that can fool multiple DNN models simultaneously, presenting a solution for detecting them.

## 4.2 Detection by coverage analysis

A different approach for detecting AEs is based on a deeper analysis of the neuron activation values in the different DNN layers. In fact, in order to force a DNN model to classify an input with a desired wrong class, AEs usually cause an overactivation of some neurons in different network layers. To identify such neurons, Rossolini et al. [32] presented a new coverage analysis methodology capable of detecting both adversarial and out-of-distribution inputs.

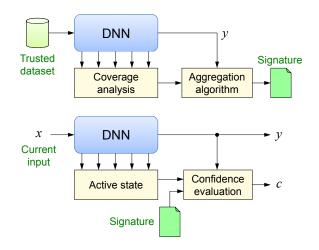

The approach works in two distinct phases: in a preliminary (off-line) phase, a trusted dataset is presented to the DNN and the neuron outputs, in each layer and for each class, are analyzed and aggregated into a set of covered states, which all together represent a sort of *signature* describing how the model responds to the trusted samples for each given class. Then, at runtime, each new input is subject to an evaluation phase, in which the activation state produced by the input in each layer is compared with the corresponding signature for the class predicted by the network. The higher the number of activation values outside the range observed during the presentation of the trusted dataset, the higher the probability that the current input is not trustworthy. The approach is schematically illustrated in Figure 6.

The nice thing about this approach is that the comparison against the signature allows computing a confidence value c distinct from the prediction score, indicating how much the current prediction can be trusted.

#### 4.3 Interpretability issues

Another problem of complex machine learning models is that they are hardly interpretable by humans. In fact, they encode their input-output function in millions of parameters and, therefore, it is not trivial to understand why a given input produces a certain output. Many people demand for transparency and precise mechanisms as a prerequisite for trust. Especially for safety-critical applications, developers cannot trust a critical decision system if it is not possible to explain the reasons that brought to that decision.

To address this issue, a new branch of research, referred to as *Explainable AI* (XAI) [36], started around 2014 with the goal of reconstructing and representing in a comprehensible fashion the features that caused an AI model to produce a given output.

#### 1:10 Can We Trust AI-Powered Real-Time Embedded Systems?

**Figure 6** Overview of the coverage-based method proposed in [32]: (top) off-line phase for producing the signature for each layer and each class; (bottom) online detection phase based on comparing the current activation states with the stored signature. It produces a confidence value *c* indicating how much the current prediction can be trusted.

Thanks to these methods, it has been found that, in some cases, a DNN learned to classify images using features that have nothing to do with the object of interest, but appear frequently in most training samples of a specific class (e.g., water for the class *ship*, snow for the class *wolf*, or even copyright tags present in most of the images of a given class). Such biases in the training data limit the generalization capabilities of a neural model and can cause wrong predictions that would be quite harmful in applications like self-driving cars or medical diagnoses.

Identifying such biases in the training set is the main objective of XAI, which in the last years proposed several methods and tools for making AI decisions more interpretable to humans [21]. For instance, Pacini et al. [23] presented X-BaD, a flexible tool for detecting biases in training sets while providing user-interpretable explanations for DNN outputs. The tool can also be used to compare the performance of different XAI methods.

# 5 Towards trustworthy Al-based systems

From the considerations presented in the previous sections, it should be clear that, although AI algorithms exhibit a great performance in several perception and control tasks, they have intrinsic weaknesses in terms of safety, security, timing predictability, and certifiability. Does it mean that complex cyber-physical systems cannot take advantage of such an amazing software technology? Fortunately, there is a promising way to exploit the power of modern deep learning algorithms in safety-critical systems.

While we cannot prevent AI algorithms from being attacked or producing unsafe results, we can take a number of countermeasures to prevent them from harming the whole system.

For instance, the level of temporal predictability, as well as the level of security of the whole system can be increased by using a suitable real-time hypervisor capable of isolating the safety-critical components from the AI-powered functions in two separated virtual machines, as described in Section 3. In this way, an attack to the AI domain cannot propagate to the high-criticality domain, which can be protected by exploiting the hardware security features available in modern computer architectures.

#### G. Buttazzo

To cope with adversarial attacks and OoD samples, the defense methods described in Section 4 are essential to detect both malicious as well as unsafe inputs that would cause a DNN to produce a wrong output. In these cases, the system must react by excluding the attacked AI component from the decision pipeline and switching to a simpler, but safer, backup control module that can bring the system into a safe state. For instance, in a self-driving car, the backup module could take control of the vehicle to stop it at the side of the road.

The approach described above has been undertaken by Biondi et al. [8] for exploiting deep learning models in safety-critical systems. The architecture includes two execution domains illustrated in Figure 7: a high-performance domain, running under Linux, and a safety-critical domain, running under the Erika Enterprise real-time kernel [1], both managed by the CLARE hypervisor [2].

**Figure 7** Architecture scheme proposed in [8], including a high-performance domain (running all the AI functions) and a safety-critical domain (running all critical control functions), managed by the CLARE hypervisor.

The high-performance domain is in charge of executing all the AI algorithms and tasks that must run under Linux, whereas the safety-critical domain runs all the vital system functions under the Erika Enterprise real-time kernel [1].

To increase the level of robustness against AEs and OoD inputs, each perceptual function is replicated by three different DNN models trained on different datasets. Each DNN also includes a coverage analyzer to provide a confidence signal (represented by the red arrow coming out from each DNN box). The three confidence signals are then integrated into an overall confidence signal, which is used to decide whether to switch to the safe controller. The three redundant DNN outputs go instead to a majority voter to resolve possible disagreements in the predictions.

An extra safety feature is represented by the presence of a *Safety Monitor*, which is in charge of detecting possible DNN outputs that could have a negative consequence on the controlled system. In fact, even in the presence of a non-malicious input, a DNN could generate an output that is not detected as unsafe by the voter and the confidence integrator, but could cause the controlled system to fail or misbehave. If such a condition is detected by the Safety Monitor, the system control is switched from the high-performance AI controller to the backup controller.

#### 1:12 Can We Trust Al-Powered Real-Time Embedded Systems?

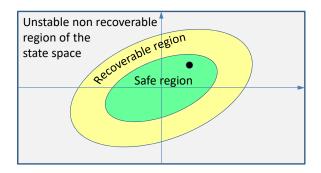

A first version of the architecture has been successfully implemented and tested on a control system for an inverted pendulum. In this case, the Safety Monitor uses a Lyapunov approach to detect when the system state exits a safe region of the state space and enters a margin region in which the stability can still be recovered by the safe controller. When this happens, the control is given to the backup controller. The AI controller is re-enabled when the system state goes back to the safe zone.

Figure 8 illustrates a simplified and qualitative representation of the state space for an inverted pendulum, where the black dot represents the current system state, the safe region is visualized in green, the recoverable region in yellow, and the unstable region in gray.

**Figure 8** Qualitative representation of the state space for an inverted pendulum. The black dot represents the current system state.

On the same line, Belluardo et al. [4] presented a safe and secure multi-domain software architecture tailored for autonomous driving.

# 6 Conclusions

This paper presented a set of problems that today prevent the use of deep learning algorithms in mission-critical systems, as self-driving vehicles, autonomous robots, and medical applications. Among them, the most relevant issues are the low predictability of modern heterogeneous architectures and the high vulnerability of AI software to cyber attacks.

Fortunately, the research community is readily reacting to address such problems and some solutions to overcome such limitations have already been proposed at different architecture levels. However, the problems are many and complex, so several issues remain unsolved and require some joint effort from the AI and the real-time research communities.

#### — References -

- 1 Erika Enterprise RTOS. URL: https://www.erika-enterprise.com/.

- 2 The CLARE Software Stack. URL: https://accelerat.eu/clare.

- 3 Luca Abeni and Giorgio Buttazzo. Resource Reservation in Dynamic Real-Time Systems. Real-Time Systems, 27(2):123–167, July 2004.

- 4 L. Belluardo, A. Stevanato, D. Casini, G. Cicero, A. Biondi, and G. Buttazzo. A Multi-domain Software Architecture for Safe and Secure Autonomous Driving. In Proc. of the 27th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA 2021), Online event, August 18–20, 2021.

- 5 Battista Biggio and Fabio Roli. Wild patterns: Ten years after the rise of adversarial machine learning. *Pattern Recognition*, 84:317–331, December 2018.

#### G. Buttazzo

- 6 Alessandro Biondi, Alessio Balsini, Marco Pagani, Enrico Rossi, Mauro Marinoni, and Giorgio Buttazzo. A Framework for Supporting Real-Time Applications on Dynamic Reconfigurable FPGAs. In Proc. of the IEEE Real-Time Systems Symposium (RTSS 2016), Porto, Portugal, November 29 December 2, 2016.

- 7 Alessandro Biondi, Daniel Casini, Giorgiomaria Cicero, Niccolò Borgioli, and Giorgio Buttazzo et al. SPHERE: A Multi-SoC Architecture for Next-generation Cyber-Physical Systems Based on Heterogeneous Platforms. *IEEE Access*, 9:75446–75459, May 2021.

- 8 Alessandro Biondi, Federico Nesti, Giorgiomaria Cicero, Daniel Casini, and Giorgio Buttazzo. A Safe, Secure, and Predictable Software Architecture for Deep Learning in Safety-Critical Systems. *IEEE Embedded Systems Letters*, 12(3):78–82, September 2020.

- 9 N. Capodieci, R. Cavicchioli, M. Bertogna, and A. Paramakuru. Deadline-Based Scheduling for GPU with Preemption Support. In Proc. of the 39th IEEE Real-Time Systems Symposium (RTSS 2018), Nashville, Tennessee, USA, December 11-14, 2018. URL: http://arxiv.org/ abs/1312.6199.

- 10 Daniel Casini, Alessandro Biondi, and Giorgio Buttazzo. Timing Isolation and Improved Scheduling of Deep Neural Networks for Real-Time Systems. Software: Practice and Experience, 50(9):1760–1777, September 2020.

- 11 Daniel Casini, Alessandro Biondi, Giorgiomaria Cicero, and Giorgio Buttazzo. Latency Analysis of I/O Virtualization Techniques in Hypervisor-Based Real-Time Systems. In *Proceedings* of the 27th IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2021), Online event, May 18–21, 2021.

- 12 R. Cavicchioli, N. Capodieci, and M. Bertogna. Memory Interference Characterization Between CPU Cores and Integrated GPUs in Mixed-Criticality Platforms. In Proc. of the 22nd IEEE International Conference on Emerging Technologies and Factory Automation (ETFA 2017), Limassol, Cyprus, September 12–15, 2017.

- 13 Giorgiomaria Cicero, Alessandro Biondi, Giorgio Buttazzo, and Anup Patel. Reconciling Security with Virtualization: A Dual-Hypervisor Design for ARM TrustZone. In Proceedings of the 18th IEEE International Conference on Industrial Technology (ICIT 2018), Lyon, France, February 20–22, 2018.

- 14 Matthieu Courbariaux, Yoshua Bengio, and Jean-Pierre David. BinaryConnect: Training Deep Neural Networks with binary weights during propagations. In Proc. of the 29th Conference on Neural Information Processing Systems (NIPS 2015), Montreal, Canada, December 7–10, 2015.

- 15 Blane Erwin. The Groundbreaking 2015 Jeep Hack Changed Automotive Cybersecurity, 2021. URL: https://fractionalciso.com/the-groundbreaking-2015-jeep-hack-changedautomotive-cybersecurity/.

- 16 Giulia Ferri, Giorgiomaria Cicero, Alessandro Biondi, and Giorgio Buttazzo. Towards the Hypervision of Hardware-based Control-Flow Integrity for Arm Platforms. In Proceedings of the Italian Conference on CyberSecurity (ITASEC 2019), Pisa, Italy, February 12–15, 2019.

- 17 Yunhui Guo. A Survey on Methods and Theories of Quantized Neural Networks. ArXiv, abs/1808.04752, 2018.

- 18 C. Liu and J. Layland. Scheduling algorithms for multiprogramming in a hard real-time environment. *Journal of the ACM*, 20(1):40–61, January 1973.

- 19 Charlie Miller and Chris Valasek. Remote Exploitation of an Unaltered Passenger Vehicle, August 10, 2015. URL: http://illmatics.com/Remote%20Car%20Hacking.pdf.

- 20 Paolo Modica, Alessandro Biondi, Giorgio Buttazzo, and Anup Patel. Supporting Temporal and Spatial Isolation in a Hypervisor for ARM Multicore Platforms. In *Proceedings of the 18th IEEE International Conference on Industrial Technology (ICIT 2018)*, Lyon, France, February 20–22, 2018.

- 21 Christoph Molnar. Interpretable Machine Learning: A Guide for Making Black Box Models Explainable, 2021. URL: https://christophm.github.io/interpretable-ml-book/.

- 22 Federico Nesti, Alessandro Biondi, and Giorgio Buttazzo. Detecting Adversarial Examples by Input Transformations, Defense Perturbations, and Voting. *IEEE Transactions on Neural Networks and Learning Systems*, August 2021.

#### 1:14 Can We Trust AI-Powered Real-Time Embedded Systems?

- 23 Marco Pacini, Federico Nesti, Alessandro Biondi, and Giorgio Buttazzo. X-BaD: A Flexible Tool for Explanation-Based Bias Detection. In Proc. of the IEEE International Conference on Cyber Security and Resilience, Online event, July 26–28, 2021.

- 24 M. Pagani, A. Biondi, M. Marinoni, L. Molinari, G. Lipari, and G. Buttazzo. A Linux-Based Support for Developing Real-Time Applications on Heterogeneous Platforms with Dynamic FPGA Reconfiguration. *Future Generation Computer Systems*, To appear.

- 25 Marco Pagani, Alessio Balsini, Alessandro Biondi, Mauro Marinoni, and Giorgio Buttazzo. A Linux-based Support for Developing Real-Time Applications on Heterogeneous Platforms with Dynamic FPGA Reconfiguration. In *Proceedings of the 30th IEEE International System*on-Chip Conference (SOCC 2017), Munich, Germany, September 5–8, 2017.

- 26 Marco Pagani, Enrico Rossi, Alessandro Biondi, Mauro Marinoni, Giuseppe Lipari, and Giorgio Buttazzo. A Bandwidth Reservation Mechanism for AXI-based Hardware Accelerators on FPGAs. In Proc. of the Euromicro Conference on Real-Time Systems (ECRTS 2019), Stuttgart, Germany, July 9–12, 2019.

- 27 Francesco Restuccia and Alessandro Biondi. Time-Predictable Acceleration of Deep Neural Networks on FPGA SoC Platforms. In Proc. of the 42nd IEEE Real-Time Systems Symposium (RTSS 2021), Online event, December 7–10, 2021.

- 28 Francesco Restuccia, Alessandro Biondi, Mauro Marinoni, and Giorgio Buttazzo. Safely preventing unbounded delays during bus transactions in FPGA-based SoC. In Proceedings of the 28th Annual Int. Symposium on Field-Programmable Custom Computing Machines (FCCM 2020), Fayetteville, Arkansas, USA, May 3–6, 2020.

- 29 Francesco Restuccia, Marco Pagani, Alessandro Biondi, Mauro Marinoni, and Giorgio Buttazzo. Is Your Bus Arbiter Really Fair? Restoring Fairness in AXI Interconnects for FPGA SoCs. ACM Transactions on Embedded Computing Systems, 18(5-51):1–22, October 2019.

- 30 Francesco Restuccia, Marco Pagani, Alessandro Biondi, Mauro Marinoni, and Giorgio Buttazzo. Modeling and analysis of bus contention for hardware accelerators in FPGA SoCs. In Proceedings of the 32nd Euromicro Conference on Real-Time Systems (ECRTS 2020), Online event, July 7–10, 2020.

- 31 Enrico Rossi, Marvin Damschen, Lars Bauer, Giorgio Buttazzo, and Jörg Henkel. Preemption of the Partial Reconfiguration Process to Enable Real-Time Computing with FPGAs. ACM Transactions on Reconfigurable Technology and Systems, 11(2):10:1–10:24, November 2018.

- 32 Giulio Rossolini, Alessandro Biondi, and Giorgio Buttazzo. Increasing the Confidence of Deep Neural Networks by Coverage Analysis. In arXiv:2101.12100 [cs.LG], January 2021. arXiv:2101.12100.

- 33 Biruk Seyoum, Alessandro Biondi, and Giorgio Buttazzo. FLORA: FLoorplan Optimizer for Reconfigurable Areas in FPGAs. ACM Transactions on Embedded Computing Systems, 18(5-73):1–20, October 2019.

- 34 Tom Simonite. AI Has a Hallucination Problem That's Proving Tough to Fix, March 12, 2018. URL: https://www.wired.com/story/ai-has-a-hallucination-problem-thats-proving-tough-to-fix/.

- 35 Christian Szegedy, Wojciech Zaremba, Ilya Sutskever, Joan Bruna, Dumitru Erhan, Ian Goodfellow, and Rob Fergus. Intriguing properties of neural networks. In Proc. of the 2nd International Conference on Learning Representations (ICLR 2014), Banff, AB, Canada, April 14–16, 2014. URL: http://arxiv.org/abs/1312.6199.

- 36 The Royal Society. Explainable AI: the basics policy briefing, 2019. URL: https:// royalsociety.org/-/media/policy/projects/explainable-ai/AI-and-interpretability -policy-briefing.pdf.

- 37 Shixin Tian, Guolei Yang, and Ying Cai. Detecting Adversarial Examples through Image Transformation. In Proceedings of the 32nd AAAI Conference on Artificial Intelligence (AAAI-18), New Orleans, Louisiana, USA, February 2—7, 2018.

# Multi-Requirement Enforcement of Non-Functional Properties on MPSoCs Using Enforcement FSMs -A Case Study

Khalil Esper  $\square$ Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Germany

# Stefan Wildermann $\square$

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Germany

#### Jürgen Teich ⊠ Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Germany

# - Abstract

Embedded system applications usually have to meet real-time, energy or safety requirements on programs typically concurrently executed on a given MPSoC target platform. Enforcing such properties, e.g., by adapting the number of processors allocated to a program or by scaling the voltage/frequency mode of involved processors, is a difficult problem to solve, especially with a typically large varying environmental input (workload) per execution. In a previous work [4], we formalized the related enforcement problem using (a) finite state machines to model enforcement strategies, (b) discrete-time Markov chains to model the uncertain environment determining the system's workload, and (c) the system response that defines the feedback for the reactive enforcer. In this paper, we apply that approach to specify and verify multi-requirement enforcement strategies and assess a case study for enforcing two independent requirements at the same time, i.e., latency and energy consumption. We evaluate and compare different enforcement strategies using probabilistic verification for the use case of an object detection application.

**2012 ACM Subject Classification** Computer systems organization  $\rightarrow$  Multicore architectures; Theory of computation  $\rightarrow$  Linear logic; Theory of computation  $\rightarrow$  Modal and temporal logics; Hardware  $\rightarrow$  Finite state machines; Computer systems organization  $\rightarrow$  Self-organizing autonomic computing; Theory of computation  $\rightarrow$  Verification by model checking; Mathematics of computing  $\rightarrow$  Probabilistic representations

Keywords and phrases Runtime Requirement Enforcement, Verification, Finite State Machine, Markov Chain, Energy Consumption, Probabilistic Model Cheking, PCTL, MPSoC

Digital Object Identifier 10.4230/OASIcs.NG-RES.2022.2

Funding This work is funded by the Deutsche Forschungsgemeinschaft (DFG, German Research-Foundation) – Project Number 146371743 - TRR 89 Invasive Computing.

#### 1 Introduction

Many, particularly embedded system applications come along with different requirements that should be met during their execution on many-core systems. One example are temperature constraints because of a limited power budget. Causes of variations include interference with other applications, i.e., due to shared resources. In addition, the workload induced by the environment input data<sup>1</sup> can vary significantly and with high uncertainty.

This paper takes care of the uncertainty of input from the environment that is typically not under the control of a system, thus the influence is exogenous. The uncertainty of execution state on an MPSoC platform is typically caused by sharing of resources on an MPSoC platform, thus endogenous. This problem can be treated systematically by techniques for isolating application programs dynamically at run-time such as invasive computing [18] and is therefore not treated here.

© Whalil Esper, Stefan Wildermann, and Jürgen Teich; licensed under Creative Commons License CC-BY 4.0

Third Workshop on Next Generation Real-Time Embedded Systems (NG-RES 2022).

Editors: Marko Bertogna, Federico Terraneo, and Federico Reghenzani; Article No. 2; pp. 2:1–2:13

**OpenAccess Series in Informatics**

OASICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

#### 2:2 Multi-Objective Enforcement Using Enforcement FSMs

As a solution, run-time requirement enforcement (RRE) techniques such as [19] have emerged. Such techniques adjust a set of configurations like voltage/frequency setting or the degree of parallelism in reaction to observed changes in the system state or input workload. Different techniques have been proposed to implement run-time managers for dynamic adaptation of program execution [5, 7, 11, 12]. Many of them have drawbacks that either no formal guarantees can be given regarding their effectiveness of holding the specified requirements or they make simplifying assumptions regarding the controller or the manycore system under control. To overcome such disadvantages, we use *finite state machines* (FSMs) to formally specify enforcement strategies, as they are expressive in specification and computation, which helps in formulating complex strategies. Furthermore, they do not make any restricting or simplifying assumptions regarding the system-under-control, and finally they can be analyzed using formal verification techniques [4].

In this respect, we proposed a methodology [4] to verify the satisfaction of requirements on non-functional properties of program executions on MPSoCs which are controlled by FSM-based RREs. A requirement is often specified by a corridor of allowed or desired values of a non-functional property of program execution, e.g., a latency or power consumption corridor. In order to quantitatively assess a RRE strategy, we specify and formally verify important verification goals, e.g., whether a RRE is able to either strictly or at least loosely stay within the bounds of one or a set of requirements. Furthermore, how many subsequent program executions could violate a given set of requirements before eventually returning into specified requirement corridors. After introducing a *discrete-time Markov chain (DTMC)* for modeling the variation of environmental input, we model the *requirement response* of an MPSoC when executing an application program as a function that specifies for each combination of environment state and enforcer output whether and which requirements are fulfilled and which are violated.

Based on the concatenation of formal models, we can define stochastic verification problems using *Probabilistic Computation Tree Logic (PCTL)* [1], a probabilistic variant of CTL, and apply stochastic model checking, i.e., PRISM [9] to analyze and compare different enforcer strategies quantitatively.

Unlike other approaches that enforce only one requirement at a time [16, 2, 14, 15, 13], our method [4] can be used to enforce more than one requirement – although this was not shown there. In this work, we therefore use the methodology in [4] to analyze enforcers for multiple independent requirements at a time. As an example, we propose multi-requirement enforcement strategies to satisfy more than one requirement (e.g., latency and energy requirements) at a time. We then assess a case study to evaluate and compare between different strategies using probabilistic formal verification based on the PRISM model checker.

The remainder of this paper is structured as follows. Section 2 introduces the formal models for specifying the enforcement FSM and the requirement response. Section 3 describes the evaluation of a proposed set of uni- and multi-requirement enforcement FSMs based on an image processing case study and discusses the verification results. Finally, in Section 4, we conclude this work.

# 2 Run-time Requirement Enforcement (RRE)

The enforcement of requirements should be achieved even under a variation of environmental inputs. Such an input can be described for each discrete periodic execution k of a program by an environment feature vector  $x(k) \in \mathcal{X}$ , where  $\mathcal{X}$  denotes the *environment space*. Runtime requirement enforcement (RRE) techniques such as [19, 3] can be used to enforce the

#### K. Esper, S. Wildermann, and J. Teich

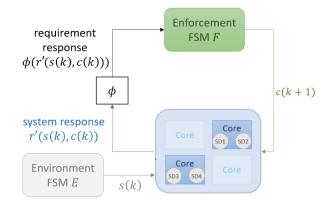

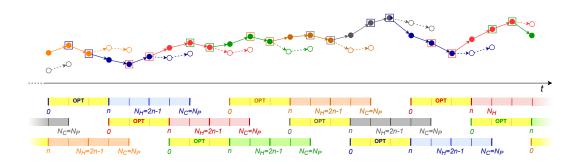

satisfaction of a set of requirements during each execution even in the presence of input variation. In the following, we term such an assignment of resources and their parametrization to execute a given program a configuration c and the set of possible system configurations to execute a program configuration space C. We consider Feedback-based RRE techniques such as [7] that react to a violation or satisfaction of a non-functional requirement  $\varphi$  based on feedback from the system-under-control and adapting the configuration c(k + 1) for the next execution (k + 1) accordingly [4]. Figure 1 illustrates the proposed model described in the following.

**Figure 1** Schematic illustration of feedback-based RRE [4].

# 2.1 Enforcement FSM F

Feedback-based RREs can be modeled by finite state machines. Following [4], a respective enforcement FSM is defined as follows:

▶ **Definition 1.** An enforcement FSM (F) is a deterministic finite state machine (Moore machine) that can be described by a 6-tuple  $(Z, z_0, I, \delta, C, \gamma)$  [4]:

- $\blacksquare$  Z is a finite set of states.

- $z_0 \in Z$  is the initial state.

- I is the input alphabet.

- $\delta$  is the transition relation:  $\delta \subseteq I \times Z \times Z$  with (i, z, z') representing a transition from state z to state z' under input i.

- $\blacksquare$  C is the output alphabet, also called configuration space.

- $\gamma$  is the output function, which maps each state to the output alphabet:  $\gamma: Z \to C$ .

An enforcement FSM is *uni-requirement* when it enforces one requirement (h = 1), and it is called *multi-requirement* when it enforces more than one requirement (h > 1).

# 2.2 Requirement Enforcement

A MPSoC platform, or system-under-control is abstracted by a single function called system response function  $r: \mathcal{X} \times C \to \mathbb{R}^h$  [4]. The system response at execution k is considered as a vector of h relevant execution qualities  $r(x(k), c(k)) = (o_1(k), \ldots, o_h(k))$ , e.g., corresponding to observed latency, power consumption, etc., during the kth execution.

### 2:4 Multi-Objective Enforcement Using Enforcement FSMs

In [17], requirements on non-functional execution qualities  $o_j$ , j = 1, ..., h are specified using intervals, e.g., resulting in two propositions  $\varphi_i^{LB}$  and  $\varphi_i^{UB}$

$$\varphi_j(o_j(k)) = \varphi_j^{LB}(o_j(k)) \land \varphi_j^{UB}(o_j(k)) = (LB_{o_j} \le o_j(k)) \land (o_j(k) \le UB_{o_j})$$

(1)

where  $LB_{o_i}$  and  $UB_{o_i}$  denote a lower, respectively upper bound on the execution quality  $o_j$ .

The system response  $r(x(k), c(k)) = (o_1(k), \ldots, o_h(k))$  is finally mapped to a requirement response using a requirement response function

$$\phi(o_1(k), \dots, o_h(k)) := \left(\varphi^{LB}(o_1(k)), \varphi^{UB}(o_1(k)), \dots, \\ \varphi^{LB}(o_h(k)), \varphi^{UB}(o_h(k))\right) \in \{0, 1\}^{2h}$$

(2)

This binary vector serves as the input to the enforcement FSM F, and thus the input alphabet is  $I \subseteq \{0,1\}^{2h}$ . Based on the requirement response, F computes as a reaction the next configuration  $c(k+1) \in C$  to enforce the desired non-functional properties for the next execution.

# 2.3 Environment FSM E

In order to apply verification techniques on a proper enforcement of requirements, we need a formal model of the environment that influences the system-under-control. Thus, the environment is modeled using a discrete-time Markov Chain called *environment FSM* [4]. However, the number of possible input values can be very large, possibly leading to a state explosion. In [4], we proposed to partition the environment space  $\mathcal{X}$  into equivalence classes or partitions p leading to the same requirement response  $\phi$  as a potential solution.

▶ **Definition 2.** An environment finite state machine E is a discrete-time Markov chain (DTMC) defined by a 3-tuple  $(S, a, \Delta)$  [4]:

- S is the finite set of states. Each  $s \in S$  is assigned exactly one partition  $p \in P$  of the environment space  $\mathcal{X}$ .

- $a: S \to [0,1]$  is a function that assigns each state  $s \in S$  its initial state probability a(s).

## 3 Multi-Requirement Enforcement Case Study

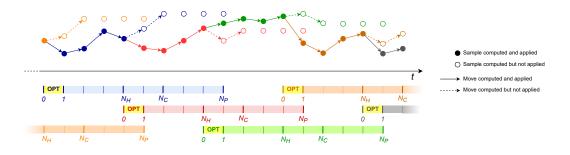

In the following, we present a simple image processing application as shown in Figure 2. The job of the object detection algorithm is to detect a given object in each image frame by applying a SIFT feature matching algorithm. Subsequently, we present different RRE variants and verify a number of PCTL verification goals related to h requirements to be enforced using probabilistic model checking.

### 3.1 Object Detection Application

The object detection application, shown in Figure 2, is an image processing application that conducts a pipelined processing of a periodic input image stream. The goal of this application is to detect a given object in each image frame by applying a scale-invariant feature transform (SIFT) matching algorithm [10]. The application consists of an actor chain. Each actor processes one input image frame k at a time. The image source (IS) actor reads in the input images periodically at a defined rate, then follows the gray-scale conversion (GS) actor, and after that the edge detection (ED) and the corner detection (CD) actors to determine

#### K. Esper, S. Wildermann, and J. Teich

respectively the edges and corners in an image. After that, the SIFT orientation (SO) actor applies invariance to image rotation. The four SIFT description actors  $SD_1$  to  $SD_4$  extract the features in an image. They can be executed in parallel on n = 4 cores, after partitioning the number of features x of a given image evenly into each actor.

For the following experiments, let each of the periodic executions of each SD actor have a latency requirement  $\varphi_L = \varphi_L^{LB} \wedge \varphi_L^{UB} = (LB_{o_L} \leq o_L) \wedge (o_L \leq UB_{o_L})$  which is typical in real-time systems and an energy consumption requirement  $\varphi_{En} = \varphi_{En}^{LB} \wedge \varphi_{En}^{UB} = (LB_{o_{En}} \leq o_{En}) \wedge (o_{En} \leq UB_{o_{En}})$ , for a latency lower bound  $LB_{o_L} = 0$  ms and an upper bound (deadline)  $UB_{o_L} = 80$  ms and an energy consumption lower bound  $LB_{o_{En}} = 0$  mJ and an energy consumption upper bound  $UB_{o_{En}} = 500$  mJ. Intuitively,  $\varphi_L^{LB} = (0 \text{ ms} \leq o_L)$  and  $\varphi_{En}^{LB} = (0 \text{ mJ} \leq o_{En})$  are always satisfied.

For the enforcement of such requirements, the execution power mode m (voltage/frequency) of the SD actors' cores through Dynamic Voltage and Frequency Scaling (DVFS) is used, and we assume, a maximum of n = 4 cores can be activated in each of m = 20 different power modes. However, during the execution of an image, we assume all cores run in the same power mode m, thus resulting in a configuration  $\langle n, m \rangle$ . Upon each execution, the output of each SD actor is then sent to the SIFT matching (SM) actor to detect common features between the given reference object and the features in the current input image. Then, the RAN-SAC (RS) actor calculates the transformation between both images based on the matched features. The image is finally delivered by an image destination (ID) actor.

**Figure 2** Object detection algorithm implemented as a graph of actors for pipelined processing of streams of images.

## 3.2 Specifying Enforcement FSMs

In the following, we introduce and compare five enforcement FSMs exemplarily, each having as many states as configurations |C|, thus  $Z = \{0, \dots, 31\}$ , the input  $i \in I = \{0, 1\}^{2h} = \{0, 1\}^4$ with  $i = \phi(r'(s, c)) = \phi(o_L, o_{En}) = ((LB_{o_L} \leq o_L), (o_L \leq UB_{o_L}), (LB_{o_{En}} \leq o_{En}), (o_{En} \leq UB_{o_{En}}))$ , an assumed initial state  $z_0 = 17$  and the configuration space C of cardinality |C| = 32.

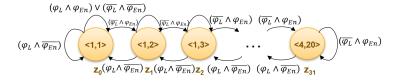

= 1-step latency-requirement enforcement FSM  $F_1$ : [3] proposes a technique called 1-step enforcement that decreases, resp. increases the current state, respectively configuration by exactly one step in case of a satisfaction ( $\varphi_L$ ), resp. violation ( $\overline{\varphi_L}$ ) of a latency requirement to be enforced. A corresponding enforcement FSM  $F_1 = (Z, z_0, I, \gamma, C, \delta_1)$  is shown in Figure 3. It has the following transition relation  $\delta_1$ :

$$z(k+1) = \begin{cases} 0 & \varphi_L \wedge (z(k) = 0) \\ z(k) - 1 & \varphi_L \wedge (z(k) \neq 0) \\ z(k) + 1 & \overline{\varphi_L} \wedge (z(k) \neq 31) \\ 31 & \overline{\varphi_L} \wedge (z(k) = 31) \end{cases}$$

(3)

**Figure 3** 1-step latency-requirement enforcement FSM  $F_1$  that only utilizes  $\varphi_L$ . Annotated to each state is the output configuration c = (n, m), consisting of number n of powered cores and power mode m.

= 1-step energy-requirement enforcement FSM  $F_2$ : Decreases, resp. increases the current state, respectively configuration reflecting the next lower, resp. higher power by exactly one step in case of a satisfaction ( $\varphi_{En}$ ), resp. violation ( $\overline{\varphi_{En}}$ ) of a energy requirement to be enforced. A corresponding enforcement FSM  $F_2 = (Z, z_0, I, \gamma, C, \delta_2)$  is shown in Figure 4. It has the following transition relation  $\delta_2$ :

$$z(k+1) = \begin{cases} 0 & \overline{\varphi_{En}} \wedge (z(k) = 0) \\ z(k) - 1 & \overline{\varphi_{En}} \wedge (z(k) \neq 0) \\ z(k) + 1 & \varphi_{En} \wedge (z(k) \neq 31) \\ 31 & \varphi_{En} \wedge (z(k) = 31) \end{cases}$$

(4)

**Figure 4** 1-step energy-requirement enforcement FSM  $F_2$  that only utilizes  $\varphi_{En}$ . Annotated to each state is the output configuration c = (n, m), consisting of number n of powered cores and power mode m.

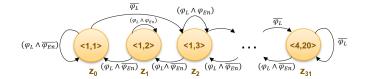

= 1-step multi-requirement enforcement FSM  $F_3$ : Stays in the current state, respectively configuration if both requirements are satisfied or none of the requirements are satisfied, and decreases the current state by exactly one step if only  $\varphi_{En}$  is violated and increases if only  $\varphi_L$  is violated. A corresponding enforcement FSM  $F_3 = (Z, z_0, I, \gamma, C, \delta_3)$  is shown in Figure 5. It has the following transition relation  $\delta_3$ :

$$z(k+1) = \begin{cases} 0 & (\varphi_L \wedge \overline{\varphi_{En}}) \wedge (z(k) = 0) \\ z(k) - 1 & (\varphi_L \wedge \overline{\varphi_{En}}) \wedge (z(k) \neq 0) \\ z(k) & ((\varphi_L \wedge \varphi_{En}) \vee (\overline{\varphi_L} \wedge \overline{\varphi_{En}})) \wedge (z(k) \neq 0) \\ z(k) + 1 & (\overline{\varphi_L} \wedge \varphi_{En}) \wedge (z(k) \neq 31) \\ 31 & (\overline{\varphi_L} \wedge \varphi_{En}) \wedge (z(k) = 31) \end{cases}$$

(5)

#### K. Esper, S. Wildermann, and J. Teich

**Figure 5** 1-step multi-requirement enforcement FSM  $F_3$  for enforcing two single-bound requirements  $\varphi_L$  and  $\varphi_{En}$ . Annotated to each state is the output configuration c = (n, m), consisting of number n of powered cores and power mode m.

• Latency-oriented multi-requirement enforcement FSM  $F_4$ : Decreases the current state by one step when only  $\varphi_{En}$  is violated, increases the current state by two steps when  $\varphi_L$ is violated, and stays in the same state otherwise. A corresponding enforcement FSM  $F_4 = (Z, z_0, I, \gamma, C, \delta_4)$  is shown in Figure 6. It has the transition relation  $\delta_5$ :

$$z(k+1) = \begin{cases} 0 & (\varphi_L \wedge \overline{\varphi_{En}}) \wedge (z(k) = 0) \\ z(k) - 1 & (\varphi_L \wedge \overline{\varphi_{En}}) \wedge (z(k) \neq 0) \\ z(k) & (\varphi_L \wedge \varphi_{En}) \wedge (z(k) \neq 0) \\ z(k) + 2 & \overline{\varphi_L} \wedge (z(k) < 30) \\ 31 & \overline{\varphi_L} \wedge (z(k) \ge 30) \end{cases}$$

(6)

**Figure 6** Latency-oriented multi-requirement enforcement FSM  $F_4$  for enforcing two single-bound requirements  $\varphi_L$  and  $\varphi_{En}$ . Annotated to each state is the output configuration c = (n, m), consisting of number n of powered cores and power mode m.

Energy-oriented multi-requirement enforcement FSM  $F_5$ : Decreases the current state by two steps when  $\varphi_{En}$  is violated, increases the current state by one step when only  $\varphi_L$ is violated, and stays in the same state otherwise. A corresponding enforcement FSM  $F_5 = (Z, z_0, I, \gamma, C, \delta_5)$  is shown in Figure 7. It has the following transition relation  $\delta_4$ :

$$z(k+1) = \begin{cases} 0 & \overline{\varphi_{En}} \wedge (z(k) \le 1) \\ z(k) - 2 & \overline{\varphi_{En}} \wedge (z(k) > 1) \\ z(k) & (\varphi_L \wedge \varphi_{En}) \wedge (z(k) \ne 0) \\ z(k) + 1 & (\overline{\varphi_L} \wedge \varphi_{En}) \wedge (z(k) \ne 31) \\ 31 & (\overline{\varphi_L} \wedge \varphi_{En}) \wedge (z(k) = 31) \end{cases}$$

$$(7)$$

**Figure 7** Energy-oriented multi-requirement enforcement FSM  $F_5$  for enforcing two single-bound requirements  $\varphi_L$  and  $\varphi_{En}$ . Annotated to each state is the output configuration c = (n, m), consisting of number n of powered cores and power mode m.

### 3.3 Verification Goals Specification

As we do not want to reason about or verify the satisfaction of verification goals during single runs or single traces of input stimuli, but depending on a DTMC model of the typically uncertain environment (i.e., E), we can use PCTL [1], a probabilistic variant of CTL, to specify stochastic verification goals. In the following,  $\mathcal{P}_{=?}[\varphi_j]$  denotes the probability of satisfying a proposition  $\varphi_j$ .

For verification, we will use PRISM [9], a probabilistic model checker, to perform verification of a number of interesting verification goals on enforcers.

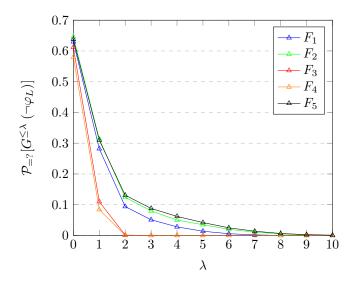

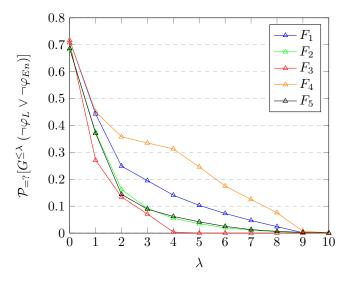

Finally, LTL formulas have a *bounded* variant in PCTL [6], which adds an upper bound  $\lambda$  on the number of successive steps or iterations in our model. In our previous work [4], we proposed and formulated a set of interesting verification goals using temporal logic. In this work, we use one of them to compare between the proposed enforcement FSMs. That being:  $\mathcal{P}_{=?}[G^{\leq \lambda} (\neg \varphi)]$  which denotes the probability of a requirement  $\varphi$  to never hold in any of  $\lambda$  consecutive executions. We will use this verification goal to verify the proposed enforcement strategies for the latency requirement  $\mathcal{P}_{=?}[G^{\leq \lambda} (\neg \varphi_L)]$ , the energy consumption requirement  $\mathcal{P}_{=?}[G^{\leq \lambda} (\neg \varphi_{En})]$ , and finally both requirements together  $\mathcal{P}_{=?}[G^{\leq \lambda} (\neg \varphi_L \lor \neg \varphi_{En})]$ .

# 3.4 Deriving Environment FSMs E

We first partition the environment space  $\mathcal{X}$  into a set of partitions P, by computing the system response  $o = (o_L, o_{En}) = r(x, c)$  for all different inputs  $x \in \mathcal{X}$  for each  $c \in C$ , and then deriving the partitions p of inputs  $x \in \mathcal{X}$  that result in the same requirement response  $\phi(r(x, c))$  for each  $c \in C$ .

For the above example application, the authors in [20] proposed to perform a design space exploration (DSE) to compute the maximum number of features  $x_{max}(UB_{o_L}, c)$  that can be processed within a given deadline  $UB_{o_L}$  in configuration c, and a single state enforcer that proactively (rather than reactively) chooses upon arrival of the kth frame always the configuration  $c \in C$  consuming the minimal amount of energy for that input. A similar DSE is conducted for the energy consumption  $o_{En}$  for an energy consumption upper bound  $UB_{o_{En}}$ .

Based on this information, we can compute the requirement response  $\phi(r(x,c))$  for each input  $x \in \mathcal{X}$  and configuration  $c \in C$  for each execution k as follows:

$$\phi(r(x,c)) = \begin{cases} (1,1,1,1) & (\varphi_L^{LB}, \varphi_L^{UB}, \varphi_{En}^{LB}, \varphi_{En}^{UB}) \\ (1,1,1,0) & (\varphi_L^{LB}, \varphi_L^{UB}, \varphi_{En}^{UB}, \overline{\varphi_{En}^{UB}}) \\ (1,0,1,1) & (\varphi_L^{LB}, \overline{\varphi_L^{UB}}, \varphi_{En}^{LB}, \varphi_{En}^{UB}) \\ (1,0,1,0) & (\varphi_L^{LB}, \overline{\varphi_L^{UB}}, \varphi_{En}^{LB}, \overline{\varphi_{En}^{UB}}) \end{cases}$$

(8)

#### K. Esper, S. Wildermann, and J. Teich

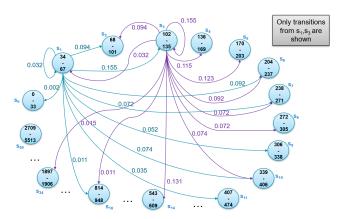

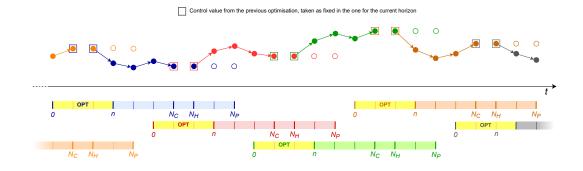

Based on this partitioning, and using a frame sequence R with |R| = 1,000 frames, we follow the procedure explained in [4] to obtain the environment FSM  $E_1$ , shown in Figure 8, which is specified after computing the partitions based on a latency requirement  $\varphi_L = \varphi_L^{LB} \wedge \varphi_L^{UB} = (LB_{o_L} \leq o_L) \wedge (o_L \leq UB_{o_L})$  and an energy consumption requirement  $\varphi_{En} = \varphi_{En}^{LB} \wedge \varphi_{En}^{UB} = (LB_{o_{En}} \leq o_{En}) \wedge (o_{En} \leq UB_{o_{En}})$ , for a latency lower bound  $LB_{o_L} = 0$ ms and an upper bound (deadline)  $UB_{o_L} = 80$  ms and an energy consumption lower bound  $LB_{o_{En}} = 0$  mJ and an energy consumption upper bound  $UB_{o_{En}} = 500$  mJ. Intuitively,  $\varphi_L^{LB} = (0 \text{ ms } \leq o_L)$  and  $\varphi_{En}^{LB} = (0 \text{ mJ} \leq o_{En})$  are always satisfied.

**Figure 8** Resulting environment FSM  $E_1$  and for an image processing algorithm for a latency lower bound  $LB_{o_L} = 0$  ms and an upper bound (deadline)  $UB_{o_L} = 80$  ms and an energy consumption lower bound  $LB_{o_{En}} = 0$  mJ and an energy consumption upper bound  $UB_{o_{En}} = 500$  mJ generated from a trace R of |R| = 1000 frames. The highest encountered number of features x (workload to be processed) per frame in the trace R is 5,513.

# 3.5 Verification Results

We specified the enforcement and environment FSMs for verification by the PRISM model checker using the PRISM modeling language [8].

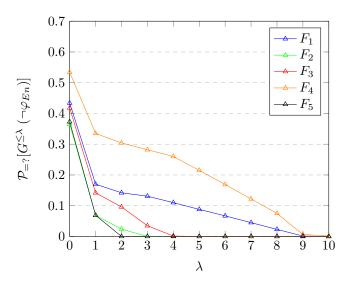

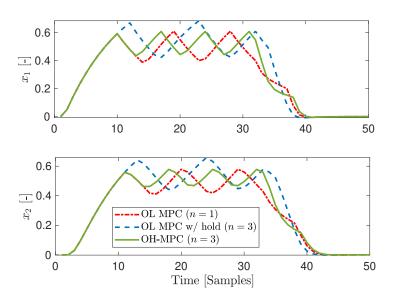

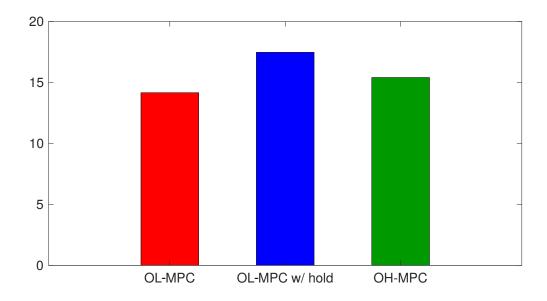

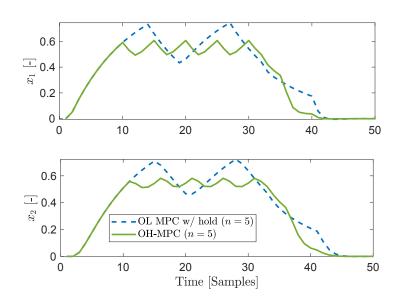

=  $\mathcal{P}_{=?}[G^{\leq \lambda}(\neg \varphi_L)]$  is the probability of  $\varphi_L$  to never hold in any of  $\lambda$  consecutive executions. Figure 9 plots this probability for increasing values of  $\lambda$  for all five introduced enforcement FSMs. We notice that  $F_2$  and  $F_5$  have the highest probabilities of violating the latency requirement among all other enforcement FSMs. This is plausible, since  $F_2$  only utilizes the energy requirement response as an input, and the multi-requirement enforcement FSM  $F_5$  is energy-oriented.

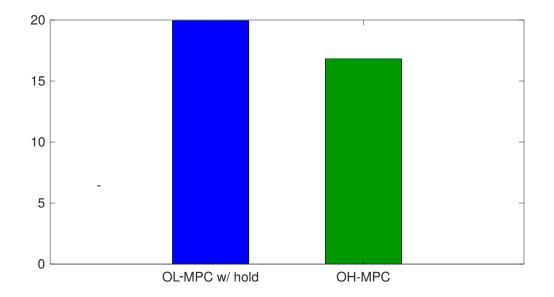

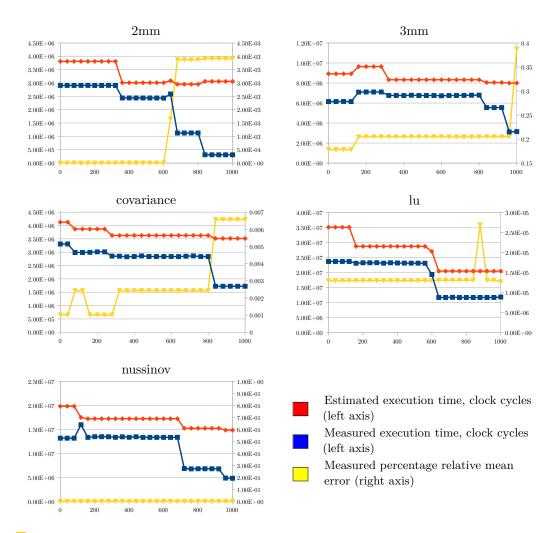

We also notice that  $F_4$  is superior regarding satisfying the satisfaction of latency requirement, since it is a latency-oriented multi-requirement enforcement FSM that jumps two steps forward when  $\varphi_L$  is violated. Finally, even  $F_1$  utilizes only the latency requirement response to transition between states, it has a higher probability of violating the latency requirement than  $F_3$  and  $F_4$ , because it goes backwards one step when  $\varphi_L$  is satisfied, unlike the multi-enforcement FSMs  $F_3$  and  $F_4$  which stay in the same state when  $\varphi_L$  is satisfied.