# 31<sup>st</sup> Euromicro Conference on Real-Time Systems

ECRTS 2019, July 9–12, 2019, Stuttgart, Germany

Edited by Sophie Quinton

LIPICS - Vol. 133 - ECRTS 2019

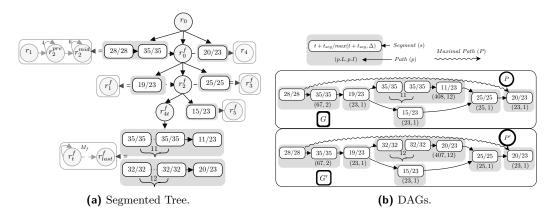

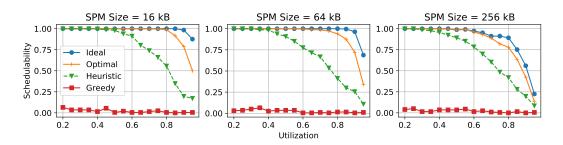

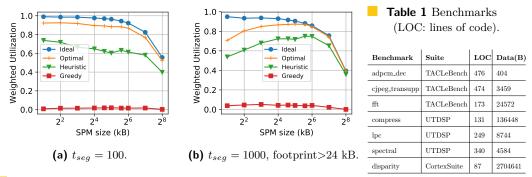

www.dagstuhl.de/lipics

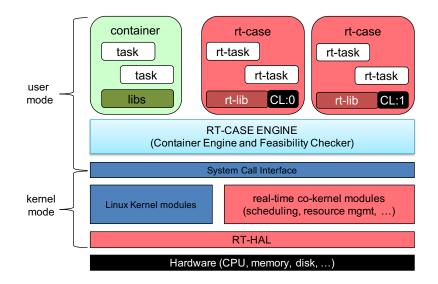

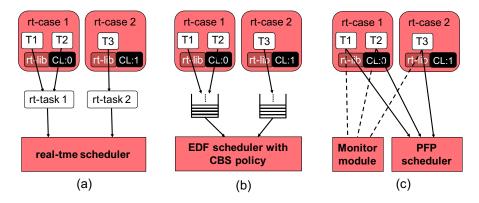

#### Editor

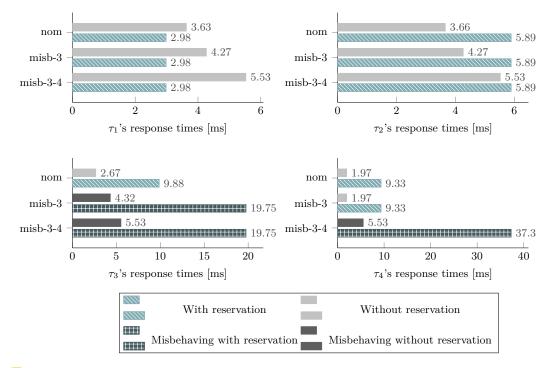

**Sophie Quinton** INRIA Grenoble Rhône-Alpes, France sophie.quinton@inria.fr

#### ACM Classification 2012

Computer systems organization  $\rightarrow$  Embedded and cyber-physical systems; Computer systems organization  $\rightarrow$  Real-time systems; Software and its engineering  $\rightarrow$  Real-time systems software; Software and its engineering  $\rightarrow$  Real-time schedulability

# ISBN 978-3-95977-110-8

Published online and open access by

Schloss Dagstuhl – Leibniz-Zentrum für Informatik GmbH, Dagstuhl Publishing, Saarbrücken/Wadern, Germany. Online available at https://www.dagstuhl.de/dagpub/978-3-95977-110-8.

Publication date July, 2019

Bibliographic information published by the Deutsche Nationalbibliothek The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at https://portal.dnb.de.

#### License

This work is licensed under a Creative Commons Attribution 3.0 Unported license (CC-BY 3.0): https://creativecommons.org/licenses/by/3.0/legalcode.

In brief, this license authorizes each and everybody to share (to copy, distribute and transmit) the work under the following conditions, without impairing or restricting the authors' moral rights: Attribution: The work must be attributed to its authors.

The copyright is retained by the corresponding authors.

Digital Object Identifier: 10.4230/LIPIcs.ECRTS.2019.0

ISBN 978-3-95977-110-8

ISSN 1868-8969

https://www.dagstuhl.de/lipics

# LIPIcs - Leibniz International Proceedings in Informatics

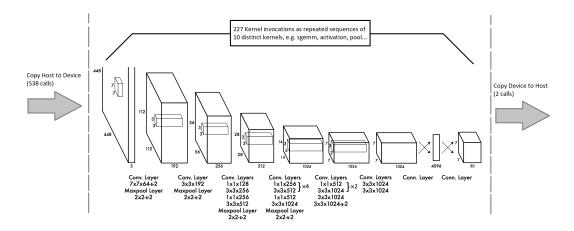

LIPIcs is a series of high-quality conference proceedings across all fields in informatics. LIPIcs volumes are published according to the principle of Open Access, i.e., they are available online and free of charge.

#### Editorial Board

- Luca Aceto (Chair, Gran Sasso Science Institute and Reykjavik University)

- Christel Baier (TU Dresden)

- Mikolaj Bojanczyk (University of Warsaw)

- Roberto Di Cosmo (INRIA and University Paris Diderot)

- Javier Esparza (TU München)

- Meena Mahajan (Institute of Mathematical Sciences)

- Dieter van Melkebeek (University of Wisconsin-Madison)

- Anca Muscholl (University Bordeaux)

- Luke Ong (University of Oxford)

- Catuscia Palamidessi (INRIA)

- Thomas Schwentick (TU Dortmund)

- Raimund Seidel (Saarland University and Schloss Dagstuhl Leibniz-Zentrum für Informatik)

### **ISSN 1868-8969**

# https://www.dagstuhl.de/lipics

# **Contents**

| Preface Sophie Quinton                                                                                                                                              | 0:vii–0:viii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Committees                                                                                                                                                          |              |

|                                                                                                                                                                     | 0:ix–0:xi    |

| DMAC: Deadline-Miss-Aware Control<br>Paolo Pazzaglia, Claudio Mandrioli, Martina Maggio, and Anton Cervin                                                           | 1:1–1:24     |

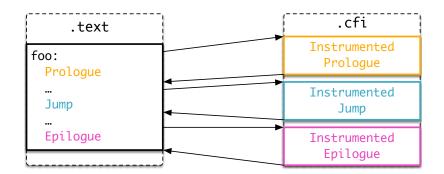

| Control-Flow Integrity for Real-Time Embedded Systems<br>Robert J. Walls, Nicholas F. Brown, Thomas Le Baron, Craig A. Shue, Hamed Okhr                             |              |

| and Bryan C. Ward                                                                                                                                                   | 2:1-2:24     |

| Simultaneous Multithreading Applied to Real Time<br>Sims Hill Osborne, Joshua J. Bakita, and James H. Anderson                                                      | 3:1-3:22     |

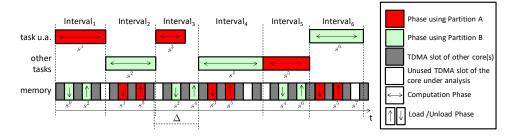

| PREM-Based Optimal Task Segmentation Under Fixed Priority Scheduling<br>Muhammad R. Soliman and Rodolfo Pellizzoni                                                  | 4:1-4:23     |

| RT-CASEs: Container-Based Virtualization for Temporally Separated<br>Mixed-Criticality Task Sets                                                                    |              |

| Marcello Cinque, Raffaele Della Corte, Antonio Eliso, and Antonio Pecchia                                                                                           | 5:1-5:22     |

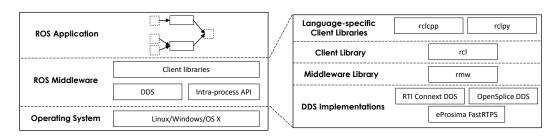

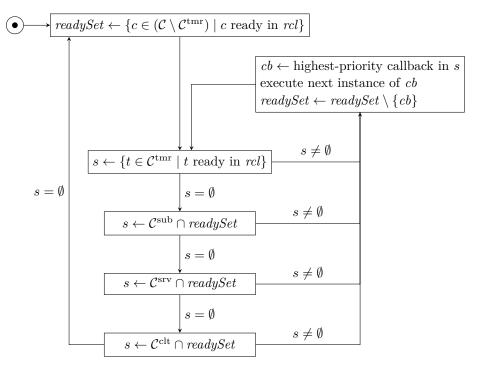

| Response-Time Analysis of ROS 2 Processing Chains Under Reservation-Based                                                                                           |              |

| Scheduling<br>Daniel Casini, Tobias Blaß, Ingo Lütkebohle, and Björn B. Brandenburg                                                                                 | 6:1-6:23     |

| Implementation of Memory Centric Scheduling for COTS Multi-Core Real-Time Systems                                                                                   |              |

| Juan M. Rivas, Joël Goossens, Xavier Poczekajlo, and Antonio Paolillo                                                                                               | 7:1–7:23     |

| Industrial Application of a Partitioning Scheduler to Support Mixed Criticality<br>Systems                                                                          | 0.1.0.00     |

| Stephen Law, Iain Bate, and Benjamin Lesage                                                                                                                         | 8:1-8:22     |

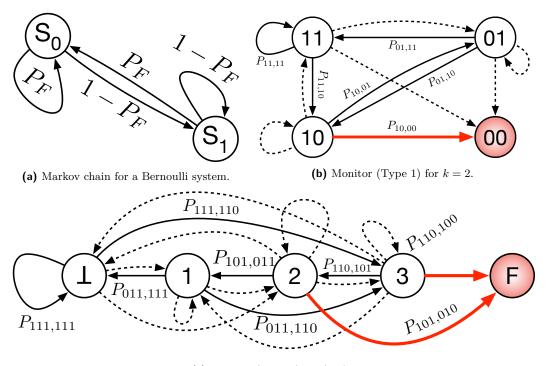

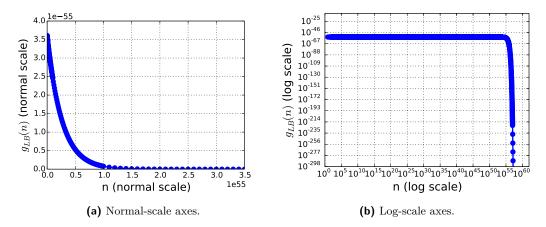

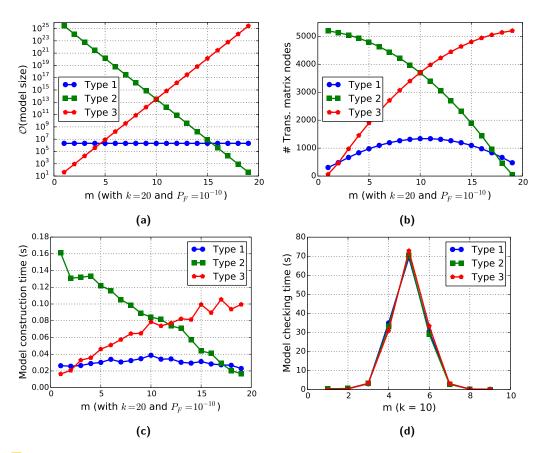

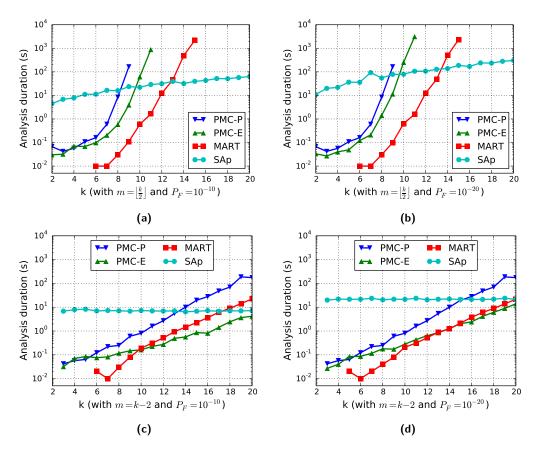

| From Iteration to System Failure: Characterizing the FITness of Periodic<br>Weakly-Hard Systems                                                                     | 0 1 0 00     |

| Arpan Gujarati, Mitra Nasri, Rupak Majumdar, and Björn B. Brandenburg                                                                                               | 9:1-9:23     |

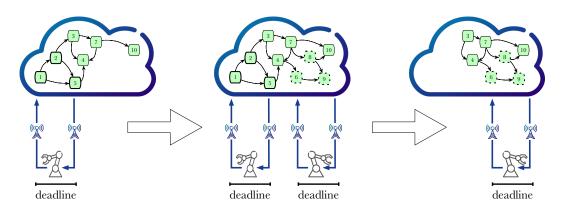

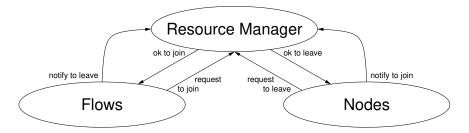

| End-To-End Deadlines over Dynamic Topologies<br>Victor Millnert, Johan Eker, and Enrico Bini                                                                        | 10:1-10:22   |

| Reliable Dynamic Packet Scheduling over Lossy Real-Time Wireless Networks<br>Tao Gong, Tianyu Zhang, Xiaobo Sharon Hu, Qingxu Deng, Michael Lemmon, and<br>Song Han | 11:1-11:23   |

| Isolation-Aware Timing Analysis and Design Space Exploration for Predictable<br>and Composable Many-Core Systems                                                    |              |

| Behnaz Pourmohseni, Fedor Smirnov, Stefan Wildermann, and Jürgen Teich $\ldots$                                                                                     | 9:1-9:24     |

| GEDF Tardiness: Open Problems Involving Uniform Multiprocessors and Affinity Masks Resolved                                                                         |              |

| Stephen Tang, Sergey Voronov, and James H. Anderson                                                                                                                 | 13:1-13:21   |

| 31st Euromicro Conference on Real-Time Systems (ECRTS 2019).<br>Editor: Sophie Quinton<br>Leibniz International Proceedings in Informatics                          |              |

| LIPICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany                                                                              |              |

| Dual Priority Scheduling is Not Optimal         Pontus Ekberg                                                                                                                                                                       | 14:1-14:9  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| NPM-BUNDLE: Non-Preemptive Multitask Scheduling for Jobs with<br>BUNDLE-Based Thread-Level Scheduling<br>Corey Tessler and Nathan Fisher                                                                                            | 15:1-15:23 |

| Scheduling Self-Suspending Tasks: New and Old Results<br>Jian-Jia Chen, Tobias Hahn, Ruben Hoeksma, Nicole Megow, and<br>Georg von der Brüggen                                                                                      | 16:1-16:23 |

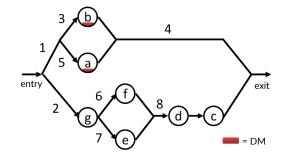

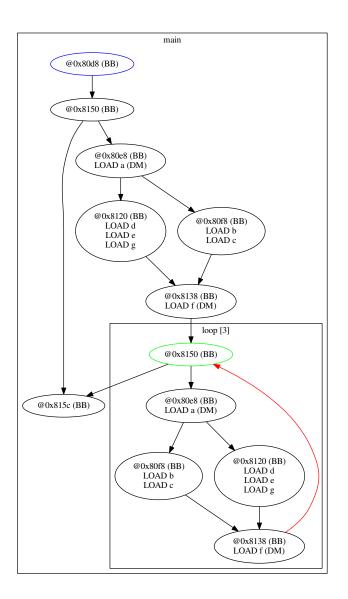

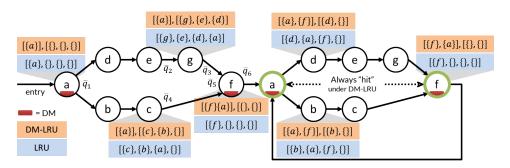

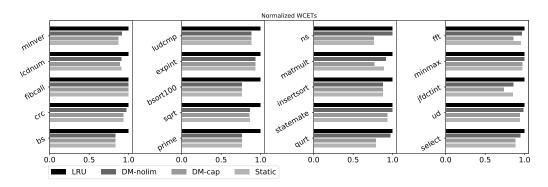

| Impact of DM-LRU on WCET: A Static Analysis Approach<br>Renato Mancuso, Heechul Yun, and Isabelle Puaut                                                                                                                             | 17:1-17:25 |

| Modeling Cache Coherence to Expose Interference<br>Nathanaël Sensfelder, Julien Brunel, and Claire Pagetti                                                                                                                          | 18:1–18:22 |

| Arbitration-Induced Preemption Delays<br>Farouk Hebbache, Florian Brandner, Mathieu Jan, and Laurent Pautet                                                                                                                         | 19:1-19:22 |

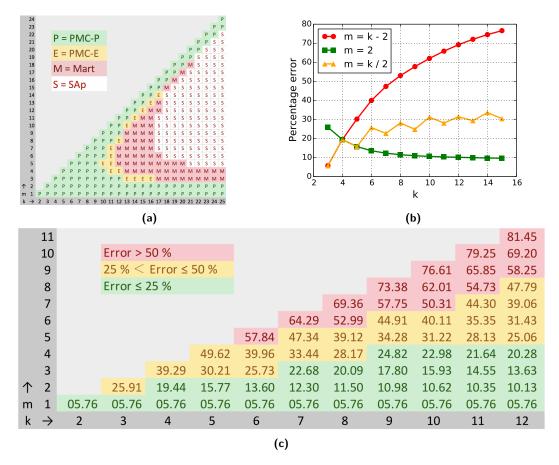

| Fast and Effective Multiframe-Task Parameter Assignment Via ConcaveApproximations of DemandBo Peng, Nathan Fisher, and Thidapat Chantem                                                                                             | 20:1-20:22 |

| Response-Time Analysis of Limited-Preemptive Parallel DAG Tasks Under<br>Global Scheduling<br>Mitra Nasri, Geoffrey Nelissen, and Björn B. Brandenburg                                                                              | 21:1-21:23 |

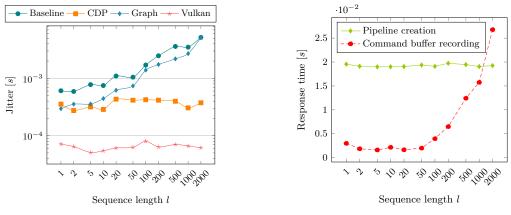

| Novel Methodologies for Predictable CPU-To-GPU Command Offloading<br>Roberto Cavicchioli, Nicola Capodieci, Marco Solieri, and Marko Bertogna                                                                                       | 22:1-22:22 |

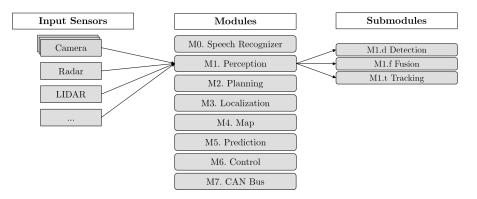

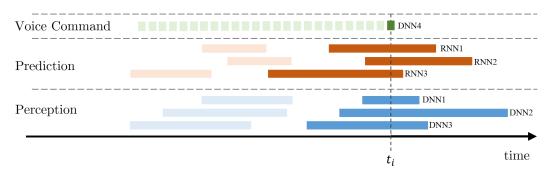

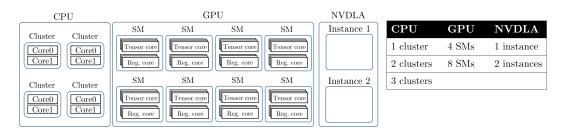

| Generating and Exploiting Deep Learning Variants to Increase Heterogeneous<br>Resource Utilization in the NVIDIA Xavier<br>Roger Pujol, Hamid Tabani, Leonidas Kosmidis, Enrico Mezzetti,<br>Jaume Abella, and Francisco J. Cazorla | 23:1-23:23 |

| A Bandwidth Reservation Mechanism for AXI-Based Hardware Accelerators on<br>FPGAs<br>Marco Pagani, Enrico Rossi, Alessandro Biondi, Mauro Marinoni,<br>Giuseppe Lipari, and Giorgio Buttazzo                                        | 24:1-24:24 |

| Hiding Communication Delays in Contention-Free Execution for SPM-Based<br>Multi-Core Architectures<br>Benjamin Rouxel, Stefanos Skalistis, Steven Derrien, and Isabelle Puaut                                                       | 25:1-25:24 |

| Slot-Based Transmission Protocol for Real-Time NoCs – SBT-NoC<br>Borislav Nikolić, Robin Hofmann, and Rolf Ernst                                                                                                                    | 26:1-26:22 |

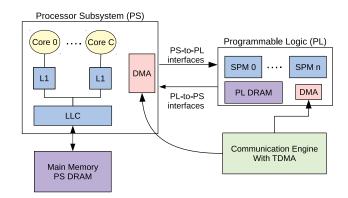

| Designing Mixed Criticality Applications on Modern Heterogeneous MPSoC<br>Platforms<br>Giovani Gracioli, Rohan Tabish, Renato Mancuso, Reza Mirosanlou,<br>Rodolfo Pellizzoni, and Marco Caccamo                                    | 27:1-27:25 |

# Message from the Chairs

Welcome to the **31<sup>st</sup> Euromicro Conference on Real-Time Systems (ECRTS 2019)** in Stuttgart, Germany. ECRTS is the premier European venue for presenting research into the broad area of real-time systems. Along with RTSS and RTAS, ECRTS ranks as one of the top three international conferences on this topic. ECRTS has been at the forefront of recent innovations in the real-time community such as artifact evaluation and open access proceedings.

For ECRTS 2019, we received **80** submissions from 19 countries, 7 of which are outside Europe and represent 37% of the submitted papers. Each submission was reviewed by at least three members of the program committee – all active researchers and experts in their field – with the help of 77 external reviewers. The submissions were evaluated according to their contribution, originality, technical correctness and writing quality. The program committee then selected, at a physical meeting of the program committee in Paris, 27 of these submissions for publication in the proceedings and presentation at the conference.

From the 27 accepted papers, three have been recognized as **outstanding papers** by the program committee and will be presented in the final session. One of these three papers will be selected as **best paper** by a dedicated committee, based on both the contribution of the paper and the presentation at the conference.

In 2016, ECRTS was the first conference on real-time systems to introduce an **artifact evaluation**, with the aim to promote reproducibility of research results. An artifact evaluation committee reviews the artifacts submitted by the authors of accepted papers who choose to do so. In 2019, eight papers (30% of the accepted papers) are marked in the proceedings with a seal indicating that their artifact has passed the repeatability test.

In 2017, ECRTS was the first conference on real-time systems to introduce an **open access publication model**, while retaining the existing quality-control measures. The open access model uses LIPIcs – Leibniz International Proceedings in Informatics, a series of high-quality conference proceedings established in cooperation with Schloss Dagstuhl, Leibniz Center for Informatics. The conference serves the research community and the public best when results are accessible to the largest audience, i.e., the research community and the public. This year again, the proceedings will be accessible free of charge for everyone.

The workshops of ECRTS, that take place the day before the main conference starts, are a key feature of the event. They are widely acknowledged to be lively and useful to the community. ECRTS 2019 will host the following workshops:

**CERTS** – 4th International Workshop on

Security and Dependability of Critical Embedded Real-Time Systems

- OSPERT 15th International Workshop on Operating Systems Platforms for Embedded Real-Time Applications

- **RTN** 17th International Workshop on Real-Time Networks

- **WATERS** 10th International Workshop on

Analysis Tools and Methodologies for Embedded and Real-time Systems

**WCET** – 19th International Workshop on Worst-Case Execution Time Analysis

31st Euromicro Conference on Real-Time Systems (ECRTS 2019). Editor: Sophie Quinton Leibniz International Proceedings in Informatics

LIPICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

ECRTS 2019 will start with a **keynote** by **Thomas Kropf**, president of corporate research and advance engineering at Bosch. A second keynote will be given by **David Monniaux**, senior researcher at CNRS and head of the PACSS team (Proofs and Code analysis for Safety and Security) at Verimag.

The **interactive session** of ECRTS 2019 is one of the most attractive events at the conference. It will feature:

- a work-in-progress session where novel ideas are introduced to the ECRTS audience;

- **journal-to-conference** presentations where work so far only published in journals can be presented to the conference audience;

- an overview of the industrial challenges discussed at the WATERS workshop to foster collaboration between academia and industry;

- an industry pitch session with industry speakers pitching their current and future problems related to real-time issues.

The interactive session will be directly followed by a poster session and reception where all participants can exchange ideas in a relaxed and friendly atmosphere. Submissions to the work-in-progress, journal-to-conference and industry pitch sessions have been evaluated separately by dedicated committees, and are not part of these published proceedings.

Thanks to our location on the premises of Bosch in Stuttgart this year, this edition of ECRTS will represent an excellent opportunity for researchers and practitioners from academia and industry to meet, interact and initiate collaborations. In addition to the special industry focus of the first day, participants will have the chance to look behind the scenes of the Bosch research campus on the second day of the conference during a guided tour, to get insights into the different fields of research conducted at Bosch.

ECRTS 2019 is the result of the hard work of many people, whose names are listed in the following pages. We are especially grateful for the contributions of the **program committee** and the **external reviewers** for carefully reviewing the submitted papers and helping us build the high-quality program of ECRTS 2019; the **artifact evaluation chairs** and the **artifact evaluators** who help this conference pave the way for reproducible research; the **work-in-progress and journal-to-conference chair** and the **workshop chairs** for their hard work in organizing these key moments of the conference; and Dagstuhl Publishing for their support in publishing these proceedings. Many thanks to the **organization committee** and **Robert Bosch GmbH** for their help with the logistics. We also thank **Sebastian Altmeyer** for sharing his experience as the ECRTS 2018 program chair, and **Gerhard Fohler** for his steady guidance and support as the Euromicro Real-Time Technical Committee Chair.

Last, but not least, we thank all the authors who submitted their work to ECRTS 2019. This conference would not exist without them and we are proud of the high quality and scientific relevance of this year's program. Let us now enjoy ECRTS 2019!

Arne Hamann and Dirk Ziegenbein General Chairs, ECRTS 2019 Sophie Quinton Program Chair, ECRTS 2019

# **Committees**

# **General Chairs**

Arne Hamann and Dirk Ziegenbein, Robert Bosch GmbH, Germany

# **Program Chair**

Sophie Quinton, INRIA Grenoble Rhône-Alpes, France

#### **Real-Time Technical Committee Chair**

Gerhard Fohler, TU Kaiserslautern, Germany

# **Organization Committee**

Steve Goddard, University of Nebraska-Lincoln, USA Martina Maggio, Lund University, Sweden

# **Artifact Evaluation Chairs**

Sebastian Altmeyer, University of Amsterdam, The Netherlands Alessandro Papadopoulos, Mälardalen University, Sweden

# Work-in-Progress and Journal-to-Conference Chair

Andrea Bastoni, SYSGO AG, Germany

#### Workshop Chairs

**CERTS** – Security and Dependability of Critical Embedded Real-Time Systems Mikael Asplund, Linköping University, Sweden Michael Paulitsch, Intel, Germany

**OSPERT** – Operating Systems Platforms for Embedded Real-Time Applications Adam Lackorzynski, TU Dresden / Kernkonzept, Germany Daniel Lohmann, Leibniz Universität Hannover, Germany

**RTN** – Real-Time Networks Guillermo Rodriguez-Navas, Nokia Bell-Labs, Israel Ramon Serna Oliver, TTTech, Austria

WATERS – Analysis Tools and Methodologies for Embedded and Real-time Systems Claire Pagetti, ONERA / IRIT-ENSEEIHT, France Selma Saidi, TU Hamburg, Germany

**WCET** – Worst-Case Execution Time Analysis Sebastian Altmeyer, University of Amsterdam, The Netherlands

#### **Program Committee**

Benny Akesson, ESI (TNO), The Netherlands Sebastian Altmeyer, University of Amsterdam, The Netherlands Jim Anderson, The University of North Carolina at Chapel Hill, USA Andrea Bastoni, SYSGO AG, Germany

31st Euromicro Conference on Real-Time Systems (ECRTS 2019).

Editor: Sophie Quinton

Leibniz International Proceedings in Informatics

Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

#### 0:x Committees

Marko Bertogna, University of Modena, Italy Alessandro Biondi, Scuola Superiore Sant'Anna, Pisa, Italy Timothy Bourke, Inria Paris, France Marius Bozga, CNRS, Verimag, Grenoble, France Björn B. Brandenburg, Max Planck Institute for Software Systems (MPI-SWS), Germany Francisco Cazorla, Barcelona Supercomputing Center, Spain Robert I. Davis, University of York, UK Johan Eker, Ericsson Research, Sweden Rolf Ernst, TU Braunschweig, Germany Sébastien Faucou, Université de Nantes, France Nathan Fisher, Wayne State University, USA Gerhard Fohler, TU Kaiserslautern, Germany Julien Forget, University of Lille, France Steve Goddard, University of Nebraska-Lincoln, USA Joël Goossens, Université libre de Bruxelles, Belgium Arne Hamann, Robert Bosch GmbH, Germany Angeliki Kritikakou, Univ Rennes, Inria, CNRS, IRISA, France George Lima, Federal University of Bahia, Brazil Martina Maggio, Lund University, Sweden Julio Medina, Universidad de Cantabria, Spain Patrick Meumeu Yomsi, CISTER, ISEP, Portugal Geoffrey Nelissen, CISTER, ISEP, Portugal Claire Pagetti, ONERA / IRIT-ENSEEIHT, France Michael Paulitsch, Intel, Germany Rodolfo Pellizzoni, University of Waterloo, Canada Isabelle Puaut, Université de Rennes 1/IRISA, France Christine Rochange, Université de Toulouse, France Jean-Luc Scharbarg, Université de Toulouse – IRIT – INPT/ENSEEIHT, France Oleg Sokolsky, University of Pennsylvania, USA Marcus Völp, SnT – University of Luxembourg, Luxembourg Haibo Zeng, Virginia Tech, USA

#### Artifact Evaluators

Muhammad Ali Awan, CISTER, ISEP, Portugal

Tobias Blaß, Robert Bosch GmbH, Germany

Fabien Bouquillon, University of Lille, France

Lélio Brun, École normale supérieure / Inria Paris, France

Paolo Burgio, University of Modena and Reggio, Italy

Daniel Casini, Scuola Superiore Sant'Anna, Pisa, Italy

Pierre-Julien Chaine, ONERA, Toulouse, France

Xiaotian Dai, University of York, UK

Frédéric Fort, University of Lille, France

Arpan Gujarati, Max Planck Institute for Software Systems (MPI-SWS), Germany

Paolo Pazzaglia, Scuola Superiore Sant'Anna, Pisa, Italy

Julius Roeder, University of Amsterdam, The Netherlands

Helena Russello, Wageningen University, The Netherlands

Stefanos Skalistis, University of Rennes / IRISA, France

Aakash Soni, IRIT/ENSEEIHT/INP Toulouse, France

#### Committees

#### **Additional Reviewers**

Aakash Soni Aaron Willcock Abhishek Singh Alexandre Venito Ali Syed Ankit Agrawal Antonio Paolillo Arpan Gujarati Bo Peng Braham Lotfi Mediouni Catherine E. Nemitz Cédric Ternon Charlotte Seidner Christoph Lambert Clara Hobbs Clément Ballabriga Corey Tessler Dakshina Dasari Daniel Casini Dirk Ziegenbein Eberle Rambo Enrico Mezzetti Falk Wurst Florian Heilmann Gautam Gala Gautham Nayak Seetanadi

Gowher Parry Hamid Tabani Ignaco Sañudo Olmedo Jacques Combaz James Robb Jaume Abella Jean-Luc Béchennec Jean-Michel Dricot Jérôme Ermont Johannes Schlatow Jordi Cardona Jordy Ruiz Jorge Martinez José Carlos Palencia Gutiérrez Juan M. Rivas Junkil Park Kevin Delmas Konstantinos Bletsas Kristin Krüger Leonidas Kosmidis Leonie Köhler Manohar Vanga Marc Boyer Marco Solieri Micaela Verucchi Mikaël Briday

Muhammad Soliman Nathan Otterness Nathanaël Sensfelder Nicola Capodieci Oana Hotescu Paolo Burgio Pedro Benedicte Radoslav Ivanov Rany Kahil Roberto Cavicchioli Robin Hofmann Rodrigo Coelho Sebastian Tobuschat Sergey Bozhko Sergey Voronov Stefanos Skalistis Stephen Tang Syed Aftab Rashid Tanya Amert Thomas Loquen Tobias Blaß Tomasz Kloda Victor Milnert Xavier Poczekajlo Zahaf Houssam Eddine

# DMAC: Deadline-Miss-Aware Control

# Paolo Pazzaglia

Scuola Superiore Sant'Anna, Pisa, Italy Department of Automatic Control, Lund University, Sweden paolo.pazzaglia@sssup.it

# Claudio Mandrioli

Department of Automatic Control, Lund University, Sweden claudio.mandrioli@control.lth.se

# Martina Maggio 回

Department of Automatic Control, Lund University, Sweden martina.maggio@control.lth.se

# Anton Cervin 回

Department of Automatic Control, Lund University, Sweden anton.cervin@control.lth.se

# – Abstract -

The real-time implementation of periodic controllers requires solving a co-design problem, in which the choice of the controller sampling period is a crucial element. Classic design techniques limit the period exploration to safe values, that guarantee the correct execution of the controller alongside the remaining real-time load, i.e., ensuring that the controller worst-case response time does not exceed its deadline. This paper presents DMAC: the first formally-grounded controller design strategy that explores shorter periods, thus explicitly taking into account the possibility of missing deadlines. The design leverages information about the probability that specific sub-sequences of deadline misses are experienced. The result is a *fixed* controller that on average works as the ideal clairvoyant time-varying controller that knows future deadline hits and misses. We obtain a safe estimate of the hit and miss events using the scenario theory, that allows us to provide probabilistic guarantees. The paper analyzes controllers implemented using the Logical Execution Time paradigm and three different strategies to handle deadline miss events: killing the job, letting the job continue but skipping the next activation, and letting the job continue using a limited queue of jobs. Experimental results show that our design proposal – i.e., exploring the space where deadlines can be missed and handled with different strategies – greatly outperforms classical control design techniques.

2012 ACM Subject Classification Computing methodologies  $\rightarrow$  Computational control theory; Computer systems organization  $\rightarrow$  Embedded software; Software and its engineering  $\rightarrow$  Real-time systems software; Theory of computation  $\rightarrow$  Stochastic control and optimization

Keywords and phrases Weakly-Hard Real-Time Systems, Deadline Miss Handling, Control Design

Digital Object Identifier 10.4230/LIPIcs.ECRTS.2019.1

Supplement Material ECRTS 2019 Artifact Evaluation approved artifact available at https://dx.doi.org/10.4230/DARTS.5.1.3

Acknowledgements All authors from Lund University are part of the ELLIIT Excellence Center. This work was partially supported by the Wallenberg Artificial Intelligence, Autonomous Systems and Software Program (WASP) funded by Knut and Alice Wallenberg Foundation.

#### 1 Introduction

Controllers are often executed alongside other tasks in a real-time platform, demanding that the scheduler ensures the timely execution of both the controller and the real-time workload that the platform should execute. Controllers can be designed taking into account resource limitations and scheduling constraints [16, 55, 54].

© Paolo Pazzaglia, Claudio Mandrioli, Martina Maggio, and Anton Cervin; licensed under Creative Commons License CC-BY 31st Euromicro Conference on Real-Time Systems (ECRTS 2019). Editor: Sophie Quinton; Article No. 1; pp. 1:1-1:24 Leibniz International Proceedings in Informatics

LIPICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

## 1:2 DMAC: Deadline-Miss-Aware Control

Studying the optimal design of a control task to be run alongside a given real-time workload can be considered an instance of the general problem of *composability*. Composability is the capability to integrate new functionalities into a preexisting system. This issue is particularly relevant in the automotive field, where the production of new vehicles requires a tight coupling of new software together with legacy code, with minimal adjustment of the original structure. In general, adding a new control task to a given taskset implies combining requirements that come from both control theory and real-time implementation. These requirements are different and often conflicting. As an example, selecting a high execution rate for the controller improves the control performance, but at the same time limits the guarantees on the timely completion of the control task code and forces the engineers to take into account overruns [13, 41]. Moreover, minimizing the monetary cost of the final system is an ever-present priority and over-provisioning resources is usually not a viable solution.

Timing constraints in real-time systems are modeled as *deadlines*, i.e., a threshold that the execution time of each task instance (job) should respect. We refer to a job that successfully completes its execution before the corresponding deadline as a *deadline hit* event. If the job could not terminate its execution before that deadline instant, we say that it *missed its deadline*. In *hard* real-time systems, missing a deadline has been always seen as a risk that must be avoided, with possibly catastrophic consequences. In reality, a limited number of deadline misses is an acceptable condition for many cyber-physical and control systems, since well-designed controllers often expose intrinsic *robustness* to timing non-idealities. Recently, *new ard* real-time system paradigm [7] to describe the case where tasks are allowed to miss a limited number of deadlines. However, often control engineers lack information about the timing behavior of the control task and the taskset structure. Understanding how a control loop behaves under deadline misses may open the door to new and better control designs.

Inspired by this challenge, in this paper we tackle the problem of designing a controller for a generic physical plant, while exploring a range of periods which have historically been avoided for co-design: we are here interested in those period values that are *shorter* than the worst-case response time of the task, thus neglecting the common hypothesis of hard deadlines. Our design problem is to run the controller alongside a preexisting taskset. Tasks are described with probabilistic execution times, ranging from a best case to a (rare) worst case value. By leveraging the flexibility of robust control design techniques, we here propose a novel method for creating an optimal fixed controller, the *Deadline-Miss-Aware Control* (DMAC), which can be implemented in a real-time task that may miss some deadlines.

The DMAC design takes into account how the controlled system behaves when different patterns of hit and missed deadlines occur. For robustness, DMAC considers a safe (pessimistic) probability of deadline miss events. Lack of scalability impedes the computation of deadline miss probabilities analytically. However, bounds are extremely pessimistic and would not aid the control design method. To overcome this limitation, we obtain an estimate of deadline miss occurrence simulating the schedule execution, drawing execution times (for all the tasks) from the corresponding probability distributions. A robust control tool, the *scenario theory* [11], provides the means to select the worst-case sequence of misses and hits from the simulations. Leveraging the scenario theory, our approach allows us to provide probabilistic guarantees for worst-case conditions both in terms of the probability of not having taken into account conditions that will eventually manifest, and in terms of the design confidence. We obtain a controller which is optimal and robust to worst-case conditions.

The analysis presented in this paper considers three different strategies for handling deadline misses: kill the job that missed the deadline, let it continue and skip the next job, or let all jobs continue until completion, but limiting the ready queue to the most

recently activated among the pending jobs (in addition to completing the one that missed the deadline). We implement the controller following the Logical Execution Time (LET) paradigm [28]. To the best of our knowledge, this is the first attempt to design an optimal controller for a real-time system that is aware of deadline misses and miss-handling strategies.

# 2 Methodology

The aim of DMAC is to provide the first control synthesis method that is *robust* both with respect to deadline misses and with respect to the strategy used to handle them. Our control design leverages knowledge of the probability that different sequences of deadline hits and misses may occur, and produces a fixed controller that is (on average) optimal with respect to a defined cost function. We obtain such knowledge by formulating a chance constrained optimization problem in a probabilistic framework, and obtaining guarantees on both the probability of neglecting important information and the confidence in the design.

# 2.1 Overview and Terminology

We present here an overview of the approach adopted for the control design and evaluation. For the application of the approach we rely on the following input data:

- $\varepsilon$ : The user selects a defined value of  $\varepsilon$ , that represents a worst case bound on the probability of carrying out the control design operations neglecting important information. We rely on the generation of sequences of deadline hits and misses, from which we select the worst case and design our controller to be robust with respect to such worst case. While  $\varepsilon$  can be selected to be as small as possible, we still need to accept a certain small probability that the next generated sequence would be worse than the worst case generated up to the current one.

- =  $1 \beta$ : The user selects a value for the confidence that one can have in the probabilistic guarantee that the approach is providing. The value of  $1 \beta$  is determined together with the value of  $\varepsilon$ , to indicate that the approach is based on a confidence  $1 \beta$  that the probability  $\varepsilon$  is the true probability of missing important information.

- Γ: The taskset that our design is targeting. We assume that additional (hard real-time) load is run alongside the controller task.

- $n_{\rm job}$ : Our control design is based on extracting timing behavior from simulations of a certain number of control jobs. The length of the sequences used for the controller design can be chosen depending on physical parameters, for example assuming that after a certain number of jobs the controller has settled. We recommend to select a value that contains at least a few hyperperiods, to capture chain effects if they happen.

- $J_{seq}$ : The cost function that is used to evaluate the produced sequences to select the worst-case sequence for the controller design.

- =  $\xi$ : The strategy used to handle a deadline miss. We consider three different strategies: killing the job that missed the deadline, letting it continue and skipping the next job, or letting it continue and enqueuing the next job (up to a maximum of one enqueued job at any point in time).

- $J_{ctl}$ : The cost function that is used to evaluate the controller behavior and compare the different deadline miss handling strategies.

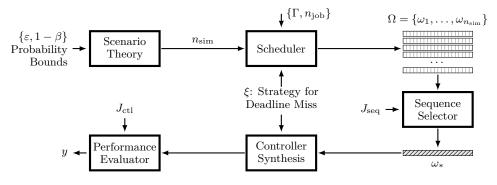

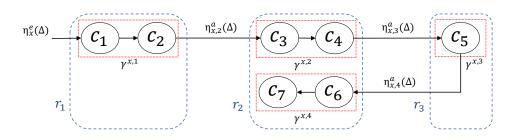

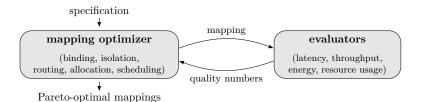

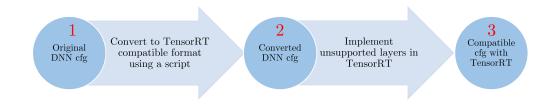

Figure 1 visually shows the different steps, inputs and outputs. As shown in the figure, our approach feeds the probability bounds ( $\varepsilon$  and  $1 - \beta$ ) to the "Scenario Theory" [11] block. The scenario theory is used in control for the design of robust controllers to handle

**Figure 1** Approach Overview.

uncertainty that is *a priori* unpredictable in the disturbance values and in the system model. In this paper we reinterpret the scenario results to enable a control synthesis strategy that uses deadline hits and misses information and provides (probabilistic) guarantees.

The scenario theory is a formal tool that determines how to analyze experimental data. In particular, we schedule our taskset extracting execution times from the corresponding probability distributions that are known in the  $\Gamma$  taskset. The theory provides us with information on how many experiments (scheduling simulations) we should execute in order for the probability that unforeseen circumstances are worse than the gathered data to be lower or equal to  $\varepsilon$  with confidence  $1 - \beta$ . We denote the number produced by the scenario theory with  $n_{\rm sim}$ . For each of the  $n_{\rm sim}$  experiments, we randomly sample the probability distributions of the task execution times, to generate a set  $\Omega = \{\omega_1, \ldots, \omega_{n_{\rm sim}}\}$  scheduling sequences, in which the control task executes for  $n_{\rm job}$  times, using strategy  $\xi$  to handle the deadline misses. Using our scheduler, we record sequences of deadline hits and misses.

We evaluate each of these sequences with a cost function  $J_{\text{seq}}$ , identifying the worst sequence  $\omega_*$ , from the control perspective. From this sequence we extract the probability of deadline hits and misses for each of the  $n_{\text{job}}$  instances of the control task and the joint probability distribution for each sequence of hits and misses needed for the control design. The controller synthesis block uses the extracted information for the control strategy design. The generated controller is then evaluated when the taskset is executed and the controller is connected to the real plant, using a cost function  $J_{\text{ctl}}$ , which allows us to compare the performance of different deadline management strategies. We can then determine the best deadline management strategy and control period for the system under analysis.

As output of our approach we obtain y, the evaluation of each tested strategy  $\xi$  for the specific problem. As a by-product, we also obtain the set of sequences  $\Omega$ . If we are not satisfied with our controller behavior, we can analyze the set of sequences to understand how to improve the control performance (i.e., for example optimize a certain task in the taskset).

#### Paper Organization

In the following, Section 3 discusses the model used for both the plant and the taskset, and Section 4 describes the behavior of the system using different deadline miss handling strategies. Section 5 presents the control design approach. In Section 6 we present the framework that we use to obtain probabilistic information about the scheduler behavior, and the scenario theory. In Section 7 we show our experimental setup and the evaluation criteria, and present our results. Section 8 discusses related work, and Section 9 concludes the paper.

# **3** System Model and Problem Definition

This section introduces the models used in the paper. Section 3.1 describes the model of the taskset executing on the hardware. Section 3.2 discusses the models of plant and control task. Finally, Section 3.3 introduces the three strategies used to handle deadline misses.

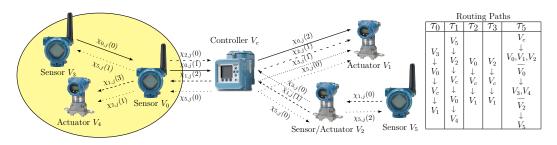

# 3.1 Taskset Model

In this paper, a real-time workload  $\Gamma$  is defined as the union of a (given) set of generic hard real-time periodic tasks, plus a real-time control task  $\tau_d$ , which is the target of our design, i.e.,  $\Gamma = \Gamma' \bigcup \{\tau_d\}$ . In this description,  $\Gamma'$  is a set of  $N_T$  periodic tasks, i.e.,  $\Gamma' = \{\tau_1, \tau_2, \ldots, \tau_{N_T}\}$ and  $\tau_d$  is an additional periodic task that contains our controller operation. We assume that each task  $\tau_i$  is independent from the others and released synchronously at a given starting instant. The tasks are scheduled using a fixed priority scheduling policy (e.g. Rate Monotonic) with preemption, and the indexing reflects their priority ordering, i.e.  $\tau_i$  has higher priority than  $\tau_j$  if i < j. In our design problem,  $\tau_d$  is the task with the lowest priority.

Each task is characterized by a tuple of parameters,  $\tau_i = (\mathcal{C}_i, f_i^{\mathcal{C}}, D_i, T_i)$ . Here,  $\mathcal{C}_i$  is a random variable that represents the task execution time, while  $f_i^{\mathcal{C}}(c)$  is its probability density function, i.e.  $\forall c \in \mathbb{N}, f_i^{\mathcal{C}}(c) = \mathbb{P}\{\mathcal{C}_i = c\}; D_i$  and  $T_i$  are deterministic values, representing respectively the task deadline and period. In accordance with the literature on real-time applications for control systems, task periods are chosen among a limited set of possible values, typically related to physical requirements of the control task [32, 39].

For each task  $\tau_i$ , we consider a discrete probability distribution  $C_i$  with  $N_i$  integer values, ranging between a Best Case Execution Time (BCET)  $C_i^{\min}$  and a Worst Case Execution Time (WCET)  $C_i^{\max}$ . Furthermore, we consider tasks that behave well in most cases, i.e., tasks whose probability density functions are skewed towards lower values. In fact, while our approach can be applied to systems with generic probability density functions, we want to capture tasks which experience occasional faulty conditions. This choice is in agreement with most works that analyze execution time distributions for real-time tasks [53]. We will generally refer to the utilization of taskset  $\Gamma'$  as the *worst-case* utilization, i.e.  $U_{\Gamma'} = \sum_{i=1}^{N_T} (C_i^{\max}/T_i)$ .

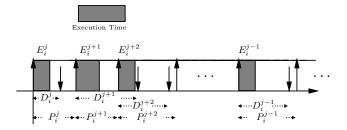

We denote each periodic instance of  $\tau_i \in \Gamma$  with the term job, and define it as  $J_{i,k}$ , with  $k = 1, 2, \ldots$  representing the job index and *i* representing the task index. For every job  $J_{i,k}$ ,  $a_{i,k}$  denotes the activation instant, and  $a_{i,k+1} - a_{i,k} = T_i$ . Since we are considering synchronous release conditions,  $\forall i, a_{i,0} = 0$  holds. In the following,  $\mathcal{R}_{i,k}$  represents the random discrete variable that models the response time of  $J_{i,k}$ . The Worst Case Response Time (WCRT) of task  $\tau_i$  is denoted as  $R_i^W$  and computed with standard techniques [33], by considering the condition where every task experiences its WCET. Similarly, the Best Case Response Time (BCRT) [43] is introduced as  $R_i^B$  and computed considering that every job executes with its BCET. Finally, in this work all tasks  $\tau_i$  in  $\Gamma'$  are schedulable, i.e.  $R_i^W \leq D_i$  for each  $\tau_i$ . However, this hypothesis will not be required for  $\tau_d$ . We will only assume that at least one job of  $\tau_d$  respects its deadline, i.e.  $R_d^B \leq D_d$ .

### 3.2 Plant and Controller Model

The plant to be controlled by  $\tau_d$  is described as a linear time invariant, multi-input multioutput system in continuous time. In line with standard assumptions, we assume the plant to be controllable and the state to be fully measurable. The plant dynamics is described as

$$\dot{\mathbf{x}}(t) = A_c \, \mathbf{x}(t) + B_c \, \mathbf{u}_c(t) + \mathbf{v}_c(t). \tag{1}$$

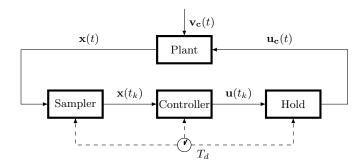

**Figure 2** Plant and controller with time-triggered sampler and hold devices.

In Equation (1), every element in bold represents a vector, while  $A_c$  and  $B_c$  are the constant matrices that encode the dynamic evolution of the system. The term  $\mathbf{x}(t)$  denotes the system state vector and  $\dot{\mathbf{x}}(t)$  its time derivative. The term  $\mathbf{u_c}(t)$  is the vector that contains the control signals. The vector  $\mathbf{v_c}(t)$  represents the plant disturbance, modeled as white noise with known covariance matrix  $R_c$ . The goal of the control is to minimize a cost function, defined as the mean value of a quadratic function of the state vector and the control vector:

$$J_{\rm ctl} = \mathbb{E}\left\{\int \mathbf{x}^{\rm T}(t)Q_{1c}\mathbf{x}(t) + \mathbf{u}_{\rm c}^{\rm T}(t)Q_{2c}\mathbf{u}_{\rm c}(t)\right\}.$$

(2)

Here,  $\mathbb{E}$  indicates the expected value, while  $Q_{1c}$  and  $Q_{2c}$  are constant positive semidefinite matrices and design parameters of the controller. They represent the trade-off between regulating  $\mathbf{x}(t)$  to zero and the cost of using the control signal  $\mathbf{u}_{\mathbf{c}}(t)$ . This cost function is used both as a controller design objective and for performance evaluation of the control task.

The plant is connected to the controller via time-triggered sampler and hold devices as shown in Figure 2. The behavior of these devices can be modeled as a dedicated task that reads and writes data with zero execution time and highest priority. The plant state is sampled every  $T_d$  time units, implying  $\mathbf{x}(t_k) = \mathbf{x}(kT_d)$ . The control job  $J_{d,k}$  is released at the same instant, i.e.  $a_{d,k} = kT_d$ , and the sensor data  $\mathbf{x}(t_k)$  is immediately available to it. Based on the state measurement, the controller computes the feedback control action  $\mathbf{u}(t_k)$ .

As an hypothesis, our control task  $\tau_d$  executes under the Logical Execution Time paradigm. Indeed, the job  $J_{d,k}$  computes the control output using  $\mathbf{x}(t_k)$  but makes it available to the actuator only at the first deadline instant after the termination of its execution. The control actuation is then held constant until the *next* update. This means that, if all jobs finish before their deadline, the following equation holds:

$$\mathbf{u}_{\mathbf{c}}(t) = \mathbf{u}(t_k), \qquad a_{d,k} + D_d \le t < a_{d,k+1} + D_d.$$

(3)

The execution time of the control task  $\tau_d$  is given as a random variable with known probability density function, and is treated equivalently to any other task in  $\Gamma'$ . On the contrary, the deadline  $D_d$  and period  $T_d$  of the control task  $\tau_d$  are part of the design. Being a LET task, we restrict our analysis to the implicit deadline case  $(D_d = T_d)$ , although in principle the approach in the paper can be applied to other relative deadlines (and corresponding output times). We further assume that the execution time properties of the controller do not change with different periods and different controller parameters (since only the values of some parameter are modified but the operations done by the control task are the same).

In the paper,  $\tau_d$  is not treated as a hard-deadline task. On the contrary, we actively look for those values of  $T_d$  such that the resulting task may miss some deadline with probability greater than zero, but still being able to guarantee a good control performance. This is to increase the system utilization, and consolidate workload on one single core. In Section 5, we present how to properly characterize the timing behavior of the controller and its synthesis.

▶ Remark 3.1. In this paper, we work under the assumption that  $\tau_d$  is the task with the lowest priority. If other tasks with priority lower than  $\tau_d$  do exist, the design proposed hereafter is still valid in principle, since those tasks cannot interfere with  $\tau_d$ . However, if this is the case, the range of possible values of  $T_d$  should be tied with the schedulability guarantees for the lower priority tasks. We reserve to analyze this more general case as a future work.

### 3.3 Handling Deadline Misses

In classic control design, the control task behavior is assumed to be strictly periodic, or at least periodic with limited reponse time jitter [16]. To provide an implementation enforcing periodicity for a controller on a real-time platform, one usually selects a period for the control task that is greater or equal than the task's WCRT. This approach is safe but can be very pessimistic. In fact, WCRT conditions may be extremely rare. Selecting the period with the mentioned constraint could limit the achievable control performance, since longer sampling periods in general mean worse disturbance rejection and smaller stability margins [15].

The approach presented in this paper explores the possibility of designing a control task with periods smaller than its WCRT, i.e.,  $T_d < R_d^W$ , thus greatly extending the design space. We remark that, with  $T_d \ge R_d^W$  there are no deadline misses, and standard approaches for the control design can be used [29, 4, 55].

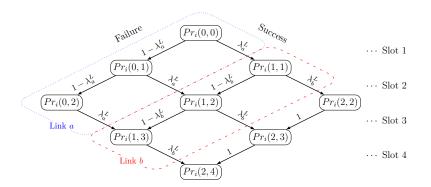

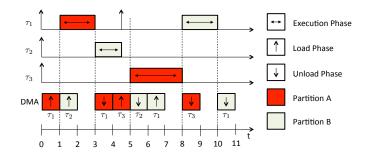

Choosing  $T_d < R_d^W$  implies the risk that the control task will miss some deadlines. A deadline miss is a timing violation that can produce unbounded response times, due to self-pushing [47], and therefore it should be properly handled. In this work, we consider three different strategies to handle deadline misses, that have previously been explored in the control community [13]: (i) to *kill* the job that has not completed at the deadline, (ii) to let the current job continue but *skip the next* job(s), and (iii) to let the job continue, placing the next job(s) in a *queue of length one*. In more detail, these strategies behave as follows:

- KILL: A control job that is not able to terminate within its deadline is dropped at the deadline instant. When a job is killed, its (partial) computation is discarded and no output is produced. We assume that this dropping mechanism has negligible overhead and internal states of the controller are not altered by the partial computation.

- SKIP-NEXT: A control job that is not able to terminate within its deadline is allowed to continue until completion. However, whenever the active job exceeds a deadline, the next instance of the control job is not activated (skipped). This is based on the idea that completing a job that has already started is preferred to starting a new one and incurring the risk that the computation runs longer than the deadline again.

- QUEUE(1): A control job that is not able to complete its execution within its deadline is allowed to continue its execution, while the following jobs are put in a queue that can contain a single element. Thus, at the activation of a new job, if there is already an active instance, the new job is enqueued, overwriting the currently existing job in the queue. Only the most recently arrived job is stored in the queue and is activated as soon as the current job completes.

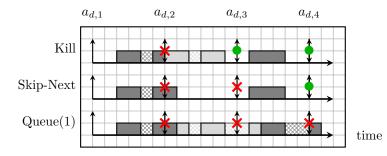

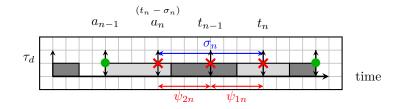

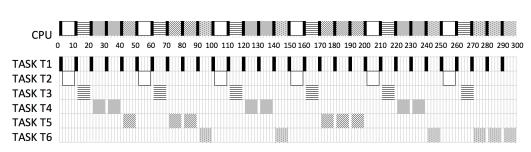

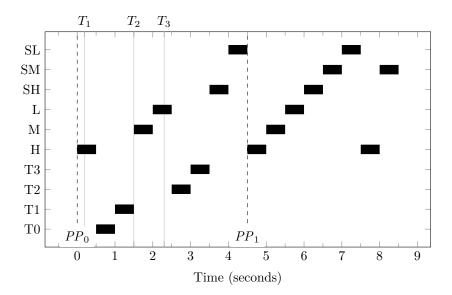

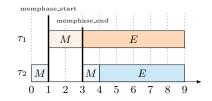

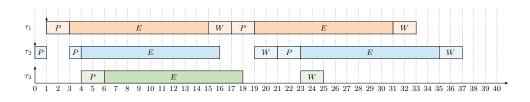

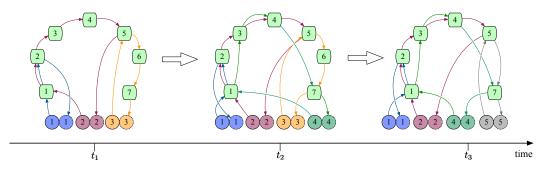

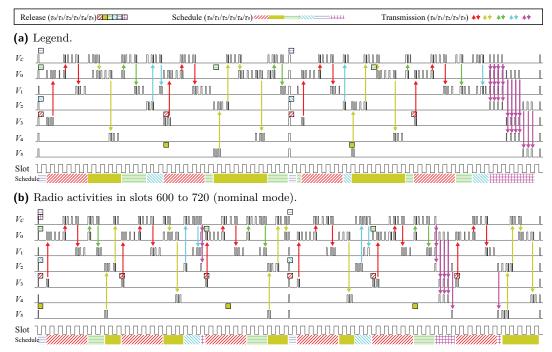

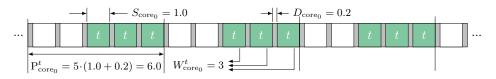

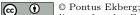

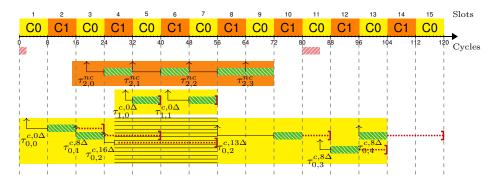

An example of a schedule under the three strategies is presented in Figure 3, where the odd jobs are shown in dark gray, while the even jobs are shown in light gray. With the Kill strategy, the first job is killed at its deadline, before completing its execution. With the

#### 1:8 DMAC: Deadline-Miss-Aware Control

**Figure 3** Schedule example using the three proposed strategies to handle deadline misses. Those jobs that missed a deadline (or are skipped) are marked with a red cross on their deadline, while a green dot identifies deadline hit events.

other two strategies, the job is given additional time in the second period, and is therefore able to complete, albeit running over time. With the Skip-Next strategy, the second job is not started, since there is an active control job that has not terminated its computation. With the Queue(1) strategy, the second job also runs over time, due to interference. In general, the Kill and Skip-Next strategies avoid self-interference conditions. This is not true for the Queue(1) strategy. However, Queue(1) may be seen as a particular case of finite buffer strategy [1], where the freshest job of the queue is always preferred, discarding the old one that has not yet started. This choice helps reducing the amount of self-interference and avoids unbounded response times. In practice, a job that is delayed more than one period by self-interference is skipped and the next one is put in the ready queue.

A sequence of consecutive control jobs may contain a certain number of jobs that are not actively contributing to the actuation  $\mathbf{u}(t)$ . This happens either with jobs that are terminated before completing their execution (killed) or with jobs not executed at all (skipped). For those jobs, a proper response time value may not be defined. Moreover, under Queue(1) strategy, it may happen that the output of a job which completes its execution after missing one or more deadlines is *overwritten* by the next job, if the latter completes before the same deadline. We therefore define the set of jobs that produce an output control that is actually provided to the physical plant, as the set of *valid* control jobs.

▶ Definition 3.2 (Valid control job). A valid control job  $\nu$  is a job that successfully completes its execution and whose generated output is not overwritten before the next deadline instant.

For each time interval [0, t), we show that is possible to extract the ordered sequence of v valid jobs, defined as  $S = \{v_1, v_2, ..., v_v\}$  (where the index does not count the passing of time) and the relation  $v \leq \lceil t/T_d \rceil$  trivially holds. The sequence of valid jobs depends on the strategy used to handle deadline misses, and will be described in Section 4. Our control design should be robust not only to the possibility of missing deadlines, but also to the different pattern of delays that are produced depending on the strategy used to handle the miss event. In the following section, we discuss how this affects the control task behavior.

# 4 Controller Behavior with Deadline Misses

In theory, choosing a shorter period allows the discrete-time controller to achieve better control performance [5]. However, real-time constraints become harder to satisfy, due to the increased interference from higher priority tasks. Since we are targeting periods shorter than the WCRT, the probability of missing a deadline for the control task is greater than

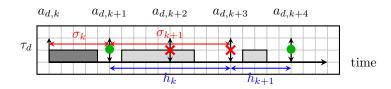

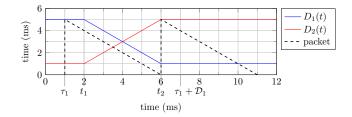

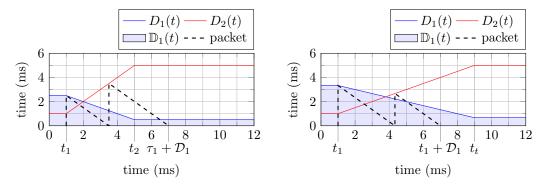

**Figure 4** Example of delay and hold values for Skip-Next strategy.

zero. A controller designed with standard techniques and subject to overrun may still display some intrinsic robustness when experiencing occasional deadline misses [13, 41]. However, the controller performance depends strongly on the deadline miss handling strategy, and may become unacceptable when the probability of missing a deadline is too high. Here we analyze the timing properties of a control task subject to deadline misses. We show that only two parameters are needed to fully characterize the miss impact. We build the rules for computing them and extract the sequence of valid control jobs.

# 4.1 Defining Delay and Hold

Missed deadlines invalidate one of the basic hypothesis of control theory, which is the periodicity of the output pattern [41]. In this work, we exploit the knowledge of deadline misses directly in the control design step. For this purpose, we need to characterize how deadline misses affect the control performance. We fully describe the effect of deadline misses of LET-based controllers with two parameters, named respectively *delay* and *hold* interval.

▶ **Definition 4.1** (Delay  $\sigma_k$ ). The delay  $\sigma_k$  experienced by a control job  $J_{d,k}$  is defined as the time interval between the activation instant of the job  $a_{d,k}$  and the instant where its control output is made available to the actuator.

In other words, the delay  $\sigma_k$  represents the time from sampling the plant state until updating the control signal. Using the above formulation,  $\sigma_k$  can only be properly defined for jobs that correctly complete their execution: if a job is killed or skipped, no delay information can be extracted, since its computation does not properly finish. We will refer to this condition as an *undefined* delay, represented with the symbol  $\infty$ . From a control perspective, the delay experienced by each (completed) job must be compensated accordingly by a predictor that computes the expected state at the output instant  $(t_k + \sigma_k)$ , using the knowledge of the current state  $\mathbf{x}(t_k)$  and the control output(s) active in that time span.

▶ Definition 4.2 (Hold interval  $h_k$ ). Given a control output computed by  $J_{d,k}$  and available at the actuator for the first time at  $t_k + \sigma_k$ , the hold interval  $h_k$  is the time interval between  $t_k + \sigma_k$  and the first instant where a new control output is made available.

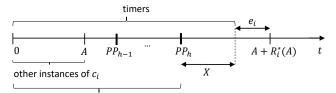

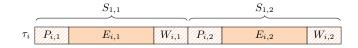

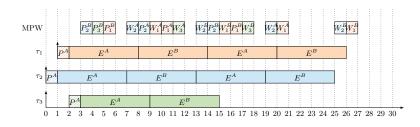

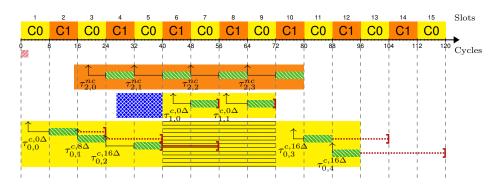

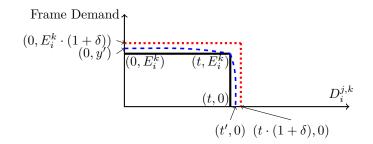

In other words, the hold interval  $h_k$  indicates the lifetime of the control signal computed by the k-th controller job and thus represents the time interval in which the computed control signal is held constant. Similarly to the delay, the definition of  $h_k$  is meaningful only for jobs that correctly complete their execution. If job  $J_{d,k}$  is killed or skipped, the hold interval is *undefined* and will be represented with the symbol  $\infty$ . Moreover, if job  $J_{d,k}$  correctly completes its execution, but its output is overwritten by the output of job  $J_{d,k+1}$  before being used, we will assign a hold value  $h_k = 0$ . Figure 4 shows an example of delay and hold intervals for a sequence of four jobs using the Skip-Next strategy.

#### 1:10 DMAC: Deadline-Miss-Aware Control

# 4.2 Computing Delay and Hold

Under ideal timing conditions – i.e., when all the deadlines of the control task are hit – the control signal produced in one period is always applied in the next period. The controller should thus compensate for a fixed delay  $\sigma_k = T_d$ . In this situation, the delay and hold have the same value and they are often not even defined as two different parameters. However, when considering deadline misses,  $\sigma_k$  and  $h_k$  may assume different values. Figure 4 shows one such example, where  $\sigma_k = 1 T_d$ ,  $h_k = 2 T_d$ ,  $\sigma_{k+1} = 2 T_d$ , and  $h_{k+1} = 1 T_d$ .

The potential differences between the delay and hold values have several consequences for the control design. First, a predictor designed for a one period delay may produce a value that is incorrect for longer delays. Second, a control signal calculated for a short hold interval could be too aggressive if applied in longer intervals. Lastly, the resulting delay-hold pattern may change across multiple control activations and depends heavily on the deadline miss handling strategy that has been chosen.

Computing the values of  $\sigma_k$  and  $h_k$  for each  $J_{d,k}$  in a schedule is then crucial for the control design process. In fact, knowing in advance the values of delay and hold interval of each job, enables the design of an optimal *time-varying* controller, that for each control job selects how to compensate the particular combination of  $\sigma$  and h for the current and following jobs. This however would require a *clairvoyant* controller, that is not practically realizable. Here we extract the possible pairs ( $\sigma_k$ ,  $h_k$ ) that may happen in a given scheduling sequence, and their associated probability, to design a fixed controller that behaves as close as possible to the ideal unrealizable one. We discuss the controller synthesis in Section 5.

Knowing  $\sigma_k$  and  $h_k$  for a given job  $J_{d,k}$ , it is also possible to determine whether the k-th control job is *valid*. This corollary follows from the definition of delay and hold interval:

# ▶ Corollary 4.3. A job $J_{d,k}$ is valid if and only if it is possible to define both its delay $\sigma_k$ and hold interval $h_k$ (i.e., they are finite numbers) and if the hold interval is greater than zero.

As a consequence, the pairs  $(\sigma_k, h_k)$  can be leveraged to extract the set of ordered valid jobs, which are the ones effectively used for building the controller. We now discuss how to compute  $\sigma_k$  and  $h_k$  for each  $J_{d,k}$  with the different miss-handling strategies. First of all, it is worth noting that the definition of  $\sigma_k$  is strictly related to the notion of response time of job  $J_{d,k}$ . In fact, the control output computed by  $J_{d,k}$  is dispatched to the actuator at the first control activation (i.e. the closest incoming deadline) that follows the termination of  $J_{d,k}$ . The delay  $\sigma_k$  of  $J_{d,k}$  can then be computed (for each strategy) as follows:

$$\sigma_k = \begin{cases} \left[ \mathcal{R}_{d,k} / T_d \right] T_d & \text{if } J_{d,k} \text{ completes} \\ \infty & \text{otherwise.} \end{cases}$$

(4)

Trivially, the maximum value for  $\sigma_k$  is  $\bar{\sigma} = \lceil \mathcal{R}_d^W / T_d \rceil T_d$ . While extracting  $\sigma_k$  requires only the knowledge of  $J_{d,k}$ , in order to compute the value of the hold interval  $h_k$  it is necessary to know the behavior of the control jobs executing after  $J_{d,k}$ , until the release of a new control update. In practice, this means that only a finite number of sub-sequences needs to be checked for characterizing all possible combinations of  $(\sigma_k, h_k)$ . Below, the equations for computing  $h_k$  for each strategy are presented in detail.

# 4.2.1 Hold Interval with Kill Strategy

Using the *Kill* strategy, the control job either finishes within one period or it is killed at its deadline. An arbitrary sequence of deadline misses may happen between two jobs that complete successfully. Denoting with  $\lambda_{k,\text{Kill}}$  the number of consecutive jobs that miss their

deadline after  $J_{d,k}$ , the hold interval associated to  $J_{d,k}$  is computed according to

$$h_k = \begin{cases} (\lambda_{k,\text{Kill}} + 1) \cdot T_d & \text{if } J_{d,k} \text{ completes} \\ \infty & \text{otherwise (if } J_{d,k} \text{ is killed}). \end{cases}$$

If  $J_{d,k}$  has been killed,  $h_k$  is not defined. Note that if some weakly hard constraint is known for  $\tau_d$ , the values of  $\lambda_{k,\text{Kill}}$  to check may be upperbounded with the maximum possible number of consecutive deadline misses of that task.

## 4.2.2 Hold Interval with Skip-Next Strategy

Using the *Skip-Next* strategy, no new job may be activated while the active one is executing. Denoting with  $\lambda_{k,\text{Skip-Next}}$  the number of skipped jobs that directly follows  $J_{d,k}$ , the hold interval of a job  $J_{d,k}$  can then be computed as

$$h_k = \begin{cases} \sigma_{k+1+\lambda_{k,\text{Skip-Next}}} & \text{if } J_{d,k} \text{ completes} \\ \infty & \text{otherwise } (J_{d,k} \text{ is skipped}). \end{cases}$$

If  $J_{d,k}$  is skipped,  $h_k$  is not defined. Intuitively, this means that for the Skip-Next strategy, the hold value of one completed job is equal to the delay of the subsequent job that completes (i.e., of the next valid job). In the example of Figure 4, job  $J_{d,k}$  terminates correctly, while  $J_{d,k+1}$  does not complete before its deadline.  $J_{d,k+2}$  is then skipped. The hold value  $h_k$  is therefore equal to the delay  $\sigma_{k+1}$  which is  $2T_d$  since the job has an overrun. The hold value  $h_{k+1}$  is equal to the delay of the next completed job  $J_{d,k+3}$ , i.e.,  $h_{k+1} = \sigma_{k+3} = T_d$ . The values that  $\lambda_{k,\text{Skip-Next}}$  may assume are upperbounded by  $\lceil R_d^W / T_d \rceil - 1$ .

# 4.2.3 Hold Interval with Queue(1) Strategy

Using the Queue(1) strategy, if a job misses its deadline, two scenarios may happen: it completes before the deadline of  $J_{d,k+1}$ , or it finishes later, then some of the subsequent jobs is skipped. In both those cases, however, the instant where the control output is published to the actuator falls exactly one period  $(T_d)$  after the activation of the next valid job. Denoting with  $\lambda_{k,\text{Queue}(1)}$  the number of (eventually) skipped jobs that directly follows  $J_{d,k}$ , the hold value  $h_k$  for job  $J_{d,k}$  is computed as follows:

$$h_{k} = \begin{cases} \sigma_{k+1} & \text{if } J_{d,k} \text{ hits its deadline} \\ \sigma_{k+1+\lambda_{k,\text{Queue}(1)}} - T_{d} & \text{if } J_{d,k} \text{ misses its deadline} \\ \infty & \text{otherwise (skipped).} \end{cases}$$

If  $J_{d,k}$  is skipped because it is removed from the queue due to a subsequent activation,  $h_k$  is not defined. Note that if  $J_{d,k}$  misses and  $J_{d,k+1}$  hits its deadline – i.e., if both the k-th and the k + 1-th control jobs complete before during the k + 1-th period – then  $\sigma_{k+1} - T_d = 0$ , and the control signal produced by  $J_{d,k}$  is never actuated. Finally, values of  $\lambda_{k,\text{Queue}(1)}$  are upperbounded by  $\lceil (R_d^W - T_d)/T_d \rceil - 1$ .

#### 5 Synthesis of Deadline-Miss-Aware Controllers

Standard digital control design assumes that samples are taken regularly and that there is a (most likely known and constant) delay from sampling to actuation [5]. When deadlines are missed, the actual hold and delay intervals will deviate from the assumed values, as explained in the previous section. This *control jitter* leads to degraded performance, and, in extreme

#### 1:12 DMAC: Deadline-Miss-Aware Control

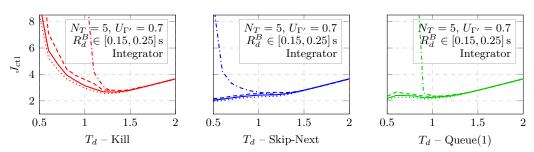

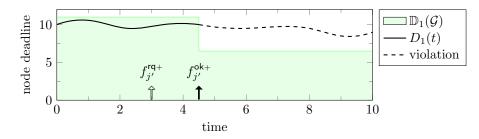

**Figure 5** Example of  $\psi_{1n}$  and  $\psi_{2n}$ .

cases, even to instability of the control loop [16]. With some knowledge about the jitter, however, it is possible to synthesize a controller that partially compensates for the timing irregularities. We outline two variants of our Deadline-Miss-Aware Control designs below.

#### 5.1 Clairvoyant Controller Synthesis

The controlled system evolution can be derived by sampling the plant only at the update instants of each valid job  $\nu_n$ , i.e. at the time where the control output produced by  $\nu_n$  is provided to the actuator. With a slight abuse of notation we will refer hereafter to the pair of delay and hold relative to  $\nu_n$  as  $(\sigma_n, h_n)$ , while its activation instant is  $a_n$ . The update instant of the control output produced by  $\nu_n$  can then be defined as  $t_n = a_n + \sigma_n$ . Moreover, the relation  $t_{n+1} = t_n + h_n$  trivially holds. For each valid control job  $\nu_n$  in sequence  $S = \{\nu_1, \nu_2, ..., \nu_v\}$ , the state evolution can be calculated as

$$\mathbf{x}(t_{n+1}) = \mathbf{x}(t_n + h_n) = A(h_n)\mathbf{x}(t_n) + B(h_n)\mathbf{u}(t_n) + \mathbf{v}(t_n),$$

(5)

where  $\mathbf{x}(t_n)$  is the state measurement sampled at time  $t_n$ ,  $\mathbf{u}(t_n)$  the control output released at time  $t_n$ , and  $\mathbf{v}(t_n)$  a discrete-time model of the plant disturbance. The discrete matrices Aand B are sampled from  $A_c$  and  $B_c$  of (1), respectively, with the step  $h_n$ . It is worth noting that different matrices  $A(h_n)$  and  $B(h_n)$  are created, depending on the possible values of  $h_n$ . In fact, a system described in this way behaves as a *switched-linear* system [48]. Computing the matrices can be done with standard procedures for sampled-data systems [5].

If the timing behavior of all jobs was completely known in advance, we would be able to design, by looking offline at the schedule, an optimal time-varying controller that minimizes the cost function (2). We call this a *clairvoyant* controller. The optimal control signal to be applied in the hold interval  $h_n$  is given by

$$\mathbf{u}(t_n) = -L_n \mathbf{x}(t_n),\tag{6}$$

where the sequence of feedback gain matrices  $\{L_n\}$  are obtained as the solution to a time-varying Riccati equation involving the sequences  $\{A(h_n)\}$ ,  $\{B(h_n)\}$ , and the sampled equivalents of the cost matrices  $Q_{1c}$  and  $Q_{2c}$ . The feedback matrices can be calculated off-line and stored in a table for on-line use.

The control law (6) cannot be implemented as it stands, though. The control action must be computed based on a state measurement that is  $\sigma_n$  time units old. Hence the controller must also predict the state from time  $t_n - \sigma_n$  to  $t_n$ . Note however that in the time interval between  $t_n - \sigma_n$  and  $t_n$ , the control actuation may not be constant, thus a slightly different modeling is needed. We will refer to the estimate of the state as  $\hat{\mathbf{x}}$ , which is computed as

$$\hat{\mathbf{x}}(t_n) = A(\sigma_n)\mathbf{x}(t_n - \sigma_n) + A(\psi_{1n})B(\psi_{2n})\mathbf{u}(t_{n-2}) + B(\psi_{1n})\mathbf{u}(t_{n-1}).$$

(7)

Here,  $\psi_{1n}$  represents the time interval in  $[t_n - \sigma_n, t_n]$  when the control actuation of the previous valid job  $\mathbf{u}(t_{n-1})$  is held constant, while  $\psi_{2n}$  is the (possible) interval where  $\mathbf{u}(t_{n-2})$  is active. For the sake of clarity, an example is shown in Figure 5. An operative procedure for computing  $\psi_{1n}$  and  $\psi_{2n}$  is given as follows:

$$\psi_{1n} = a_n + \sigma_n - (a_{n-1} + \sigma_{n-1}), \qquad \psi_{2n} = a_{n-1} + \sigma_{n-1} - a_n. \tag{8}$$

# 5.2 Robust Controller Synthesis

The clairvoyant controller has two drawbacks. First of all, it relies on exact knowledge of the execution of the system, ahead of time. This is only possible in very special circumstances. The other drawback is that it is time varying, which is more complicated to implement and requires extra memory to store the time-varying feedback gain and prediction matrices. A more realistic approach is instead to design a fixed, *robust* controller, based on the statistical properties of the system.

Again starting from the sampled system description (5), we can instead solve a *stochastic* Riccati equation [38] based on the possible values of  $A(h_n)$  and  $B(h_n)$  and their relative frequency in the schedule during the execution of the system. The control law is then

$$\mathbf{u}(t_n) = -L\,\mathbf{x}(t_n),\tag{9}$$

where  $\bar{L}$  is a *fixed* gain matrix obtained from the solution to the stochastic Riccati equation

$$\bar{X} = \mathbb{E} \left\{ \begin{bmatrix} A(h_n)^{\mathrm{T}} \\ B(h_n)^{\mathrm{T}} \end{bmatrix}^{\mathrm{T}} \bar{S} \begin{bmatrix} A(h_n)^{\mathrm{T}} \\ B(h_n)^{\mathrm{T}} \end{bmatrix} + \begin{bmatrix} Q_1(h_n) & Q_{12}(h_n) \\ Q_{12}(h_n)^{\mathrm{T}} & Q_2(h_n) \end{bmatrix} \right\}$$

$$\bar{S} = \bar{X}_{11} - \bar{L}^{\mathrm{T}} \bar{X}_{22} \bar{L}$$

$$\bar{L} = \bar{X}_{22}^{-1} \bar{X}_{12}^{\mathrm{T}}.$$

This would be the optimal fixed-gain control law if the matrices  $A(h_n)$  and  $B(h_n)$  were random and independent from job to job. In reality, there is time dependence between the hold intervals due to the scheduling algorithm, and the control law is hence only sub-optimal.

The predictor (7) must also be modified to work with statistics rather than known-ahead values. The state can be predicted using expected value calculations as

$$\hat{\mathbf{x}}(t_n) = \mathbb{E}\left\{A(\sigma_n)\right\} \mathbf{x}(t_n - \sigma_n) + \mathbb{E}\left\{A(\psi_{1n})B(\psi_{2n})\right\} \mathbf{u}(t_{n-2}) + \mathbb{E}\left\{B(\psi_{1n})\right\} \mathbf{u}(t_{n-1}).$$

(10)

Again, the predictor will only be sub-optimal due to the time-dependence induced by the scheduling algorithm.

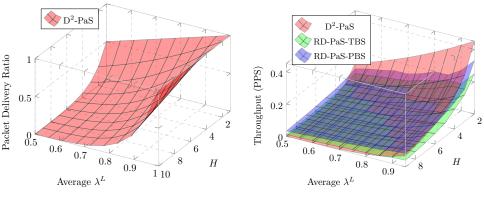

# 5.3 Controller Synthesis Example

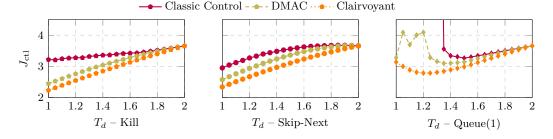

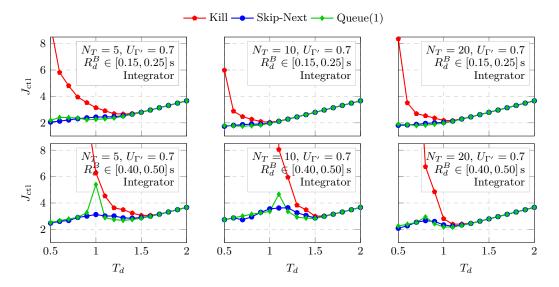

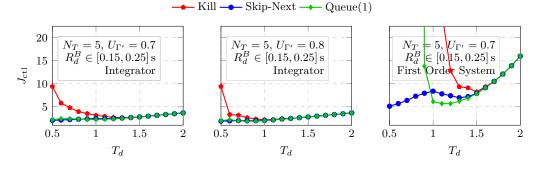

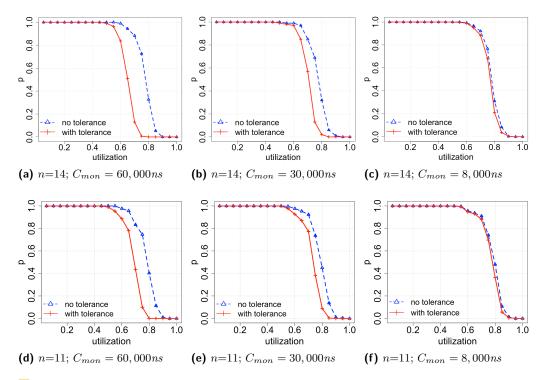

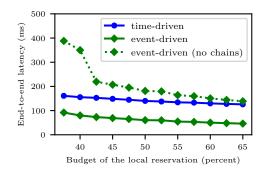

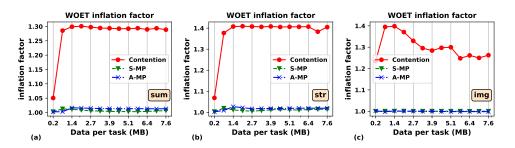

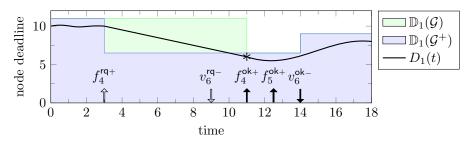

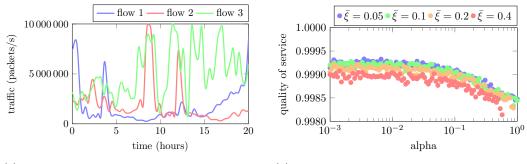

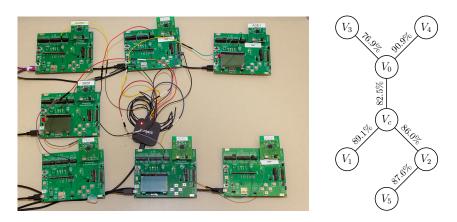

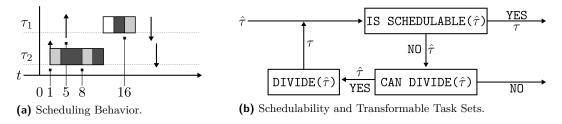

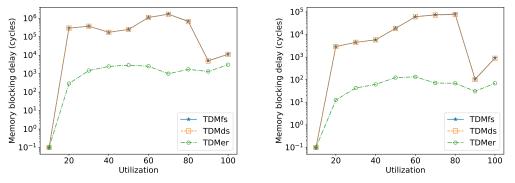

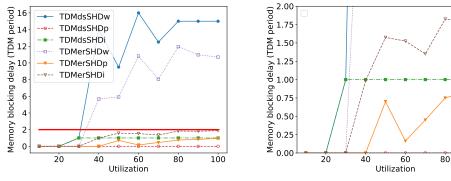

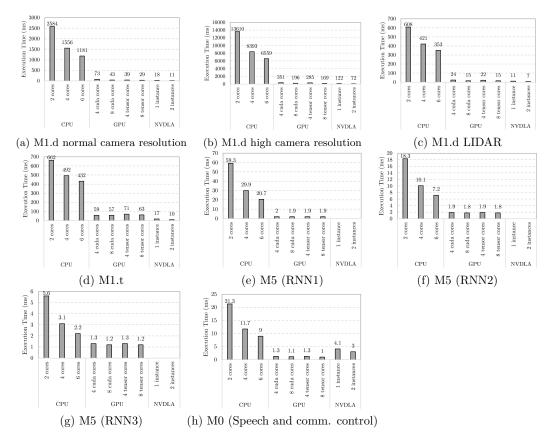

The synthesis methods presented above are illustrated in a simple control example, which was used to evaluate the performance of a standard (non-deadline-miss-aware) controller under various overrun strategies in [13]. The plant to be controlled is an integrator process described by the parameters  $A_c = 0$ ,  $B_c = 1$ ,  $Q_{1c} = 1$ ,  $Q_{2c} = 0.1$  and  $R_c = 1$ . The plant is controlled by a control task with stochastic execution times, executing alone in a CPU. The execution time may assume value equal to 1 s with probability 0.8, or uniformly distributed in the interval (1,2] with combined probability 0.2. For periods ranging between 1 and 2, we compare the resulting performance under the Kill, Skip-Next, and Queue(1) strategies in Figure 6. Since  $J_{ct1}$  is defined as a cost, lower values in the graph mean better performance.

**Figure 6** Control synthesis example: single task with deadline misses.

For each configuration, a standard controller (designed assuming no missed deadlines), a robust controller, and a clairvoyant controller are designed, and the performance of each controller, measured in terms of the cost function (2), is evaluated using JitterTime [14] in a simulation of 100,000 jobs. It can be noted that there is a strict ordering from the worst performance under standard control to the best performance under clairvoyant control, as expected. This means that designing control strategies that take into account deadline misses is beneficial in all cases. The DMAC design does not achieve the optimal cost that the clairvoyant design is able to achieve, but systematically beats classical control design due to its delay and hold compensation.

As the period is decreased from 2 to lower values, the Kill and Queue(1) strategies initially behave similarly, with decreasing cost. In fact, in the case of a miss followed by a deadline hit, the Kill and Queue(1) strategies have the same behavior (since the output of the late-completed job under Queue(1) is overwritten by the completion of the next one). Skip-Next initially has an increase in cost due to the waste of resources when a very small overrun leads to a whole period being skipped. For smaller task periods, Queue(1) suffers performance degradation and even instability ( $J_{ctl} \rightarrow \infty$ ) due to the lag introduced by the queuing. The Kill and Skip-Next strategies perform the best at  $T_d = 1$ , with very similar results for this example.

It should be noted that the results are problem dependent, and it is hard to judge whether Kill or Skip-Next works the best in general. In all examples, however, we have found that better performance can be achieved by shortening the period and allowing a few deadline misses. Some tests that include higher-priority tasks  $\Gamma'$  are presented later in Section 7.

# 6 Stochastic Analysis

Section 5 introduced a control design technique that exploits information about the probability of sequences of deadline hits and misses for the control job. Here, we provide a framework to robustly estimate these probabilities, and at the same time preserve a pessimistic bound that allows us to mitigate the effect of worst-case conditions. We formulate the estimation problem as a chance-constrained optimization problem [37], i.e., an optimization problem where we look for the probabilities of different sequences of hits and misses given the worst-case realization of the uncertainty inherently present in the taskset execution.

Analytical approaches extracting the probability of hits and misses for a schedule of jobs are either extremely pessimistic [17] or have a high computational complexity [51]. This limits the applicability of these techniques in non-trivial cases. Moreover, there are few works dealing with joint probabilities of consecutive jobs, like [49], but they still lack of scalability.

To handle the scalability issue, we adopt a simulation-based approach, backed up by the scenario theory [11], that empirically performs the uncertainty characterization, and provides formal guarantees on the robustness of the resulting estimation. The scenario theory allows us to exploit the fact that simulating the taskset execution (with statistical significance) is less computationally expensive than an analytical approach that incurs into the problem of combinatorial explosion of the different possible uncertainty realizations. In practice, this means that we: (i) sample the execution times from the probability distributions specified for each task,  $f_i^{\mathcal{C}}(c)$ , (ii) schedule the tasks, checking the resulting set of sequences  $\Omega$ , and (iii) find the worst-case sequence  $\omega_*$  based on the chosen cost function. The probabilities of sequences of hits and misses are then computed based on this sequence, and used in the design of the controller to be robust with respect to the sequence. We use the scenario theory to quantify, according to the number of extracted samples, the probability  $\varepsilon$  of not having extracted the *true* worst-case sequence and the confidence in the process  $1 - \beta$ . Scenario theory has for example found use in the management of energy storage[20].

# 6.1 Scenario Theory

The scenario theory has been developed in the field of robust control to provide robustness guarantees for convex optimization problems in presence of probabilistic uncertainty. In these problems, accounting for all the possible uncertainty realization might be achieved analytically, but is computationally too heavy or results in pessimistic bounds. The scenario theory proposes an empirical method in which samples are drawn from the possible realizations of uncertainty, finding a lower bound on the number of samples. It provides statistical guarantees on the value of the cost function with respect to the general case, provided that the sources of uncertainty are the same.

One of the advantages of this approach is that there is no need to enumerate the uncertainty sources, the only requirement being the possibility to draw representative samples. This eliminates the need to make assumptions on the correlation between the probability of deadline misses in subsequent jobs. If interference is happening between the jobs, this interference empirically appears when the system behavior is sampled. While there is no requirement on subsequent jobs interfering with one another, there is a requirement that different sequences are independent (i.e., each sequence represents an execution of the entire taskset of a given length, in the same or possibly different conditions). Taking the worst observed case in a set of experiments, the scenario theory allows us to estimate the probability that something worse than what is observed can happen during the execution of the system.

Specifically, for a sequence  $\omega$  we define a cost function  $J_{seq}(\omega)$ , that determines when we consider a sequence worse than another (from the perspective of the controller execution). Denoting with  $\mu_{tot}(\omega)$  the total number of job skips and deadline misses that the control task experienced in  $\omega$ , and with  $\mu_{seq}(\omega)$  the maximum number of consecutive deadline misses or skipped jobs in  $\omega$ , we chose to use as a cost function the following expression:

$$J_{seq}(\omega) = \mu_{tot}(\omega)\,\mu_{seq}(\omega) \tag{11}$$

to determine the worst-case sequence of hits and misses. Given a set of sequences  $\Omega = \{\omega_1, \ldots, \omega_{n_{\text{sim}}}\}\)$ , we select  $\omega_* = \arg \max_{\omega \in \Omega} J_{seq}(\omega)$ . The choice of the cost function is anyhow not-univocal. For instance, other viable alternatives would be: (i) the number of subsequences of a given length with at least a given number of deadline misses, or (ii) the shortest subsequence with more than a given number of deadline misses.

#### 1:16 DMAC: Deadline-Miss-Aware Control

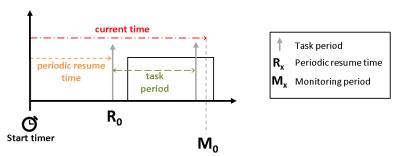

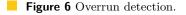

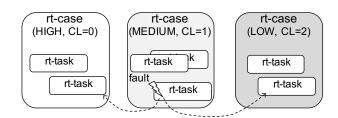

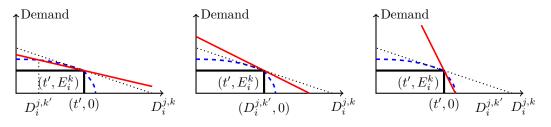

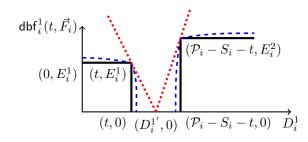

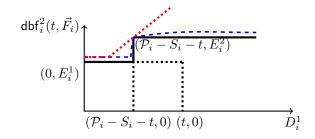

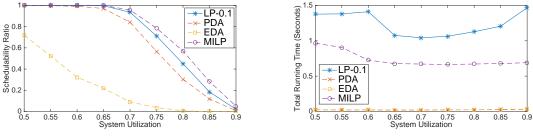

## 6.2 Formal Guarantees